Expanded CORDIC (FX, DFX, FP):

- Fixed Point (FX) and Floating Point (FP) hyperbolic engine, powering, logarithm:

The fully parameterized iterative architectures are implemented in Fixed Point and Floating Point Arithmetic. The word size is customizable.

- Architectures (FX, FP):

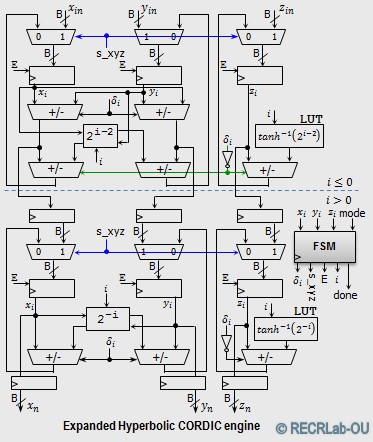

- Expanded hyperbolic CORDIC engine

- Natural Logarithm architecture (lnx) based on the expanded hyperbolic CORDIC engine

- Powering architecture (x^y) based on the expanded hyperbolic CORDIC engine

- Code/documentation:

- Papers: FP paper FX paper

- Generic VHDL implementation (stand-alone IPs): Powering, Logarithm, and expanded hyperbolic CORDIC (Source Code)

- Hardware testing and verification: MATLAB scripts, TCL scripts, testbenches, etc

- Architectures (FX, FP):

- Dual Fixed Point (DFX) CORDIC: circular, hyperbolic engines, powering and logarithm circuits:

The following fully parameterized iterative architectures are implemented in Dual Fixed Point Arithmetic. The format (word size, p0,p1) is customizable.

- Architectures (DFX):

- Expanded circular CORDIC engine

- Expanded hyperbolic CORDIC engine

- Natural Logarithm architecture (lnx) based on the expanded hyperbolic CORDIC engine

- Powering architecture (x^y) based on the expanded hyperbolic CORDIC engine

- Code/Documentation:

- Paper: DFX paper

- VHDL implementation (stand-alone IP), Vivado projects, test files (testbenches, MATLAB scripts, TCL scripts, etc): DFX CORDIC

- Architectures (DFX):

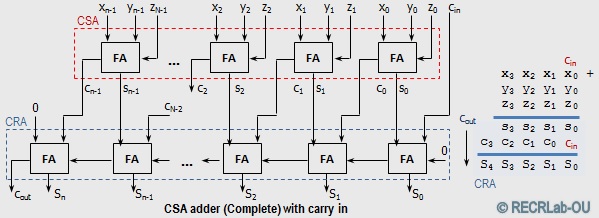

Parameterized CSA (Carry Save Adder) Units:

The following custom units (for unsigned integers) are fully parameterized architectures. Three units are presented:

- csa_complete: N-bit addition of 3 numbers. It includes CSA + RCA adders.

- csa_complete_cin: N-bit addition of 3 numbers with carry in. It includes CSA + RSA adders.

- csa_mult: NxM multiplication of 2 numbers based on CSA adders - Fully Combinational.

VHDL implementations (stand-alone IPs): Generic CSA Units VHDL IPs

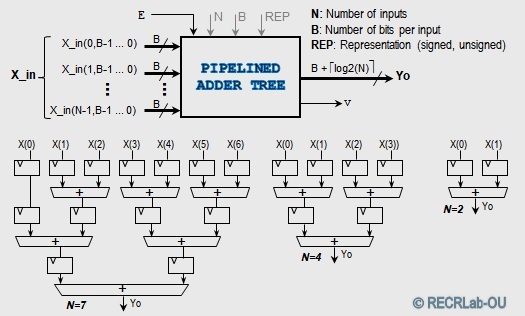

Parameterized Adder Tree with enable:

The following custom Pipelined Adder Tree core is a fully parameterized architecture.

VHDL implementations (stand-alone IPs): Generic Adder Tree with enable VHDL IP

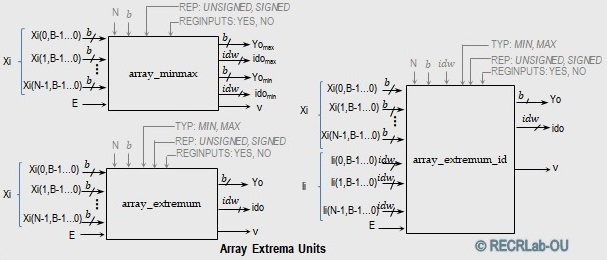

Parameterized Integer Array Extrema Units:

The following custom units are fully pipelined architectures. Three units are presented:

- array_extremum: Get the maximum or minimum of an n-element array. Indices generated internally.

- array_extremum_id: Get the maximum or minimum of an n-element array. Indices fed externally.

- array_minmax: Get the maximum and minimum of an n-element array. Indices generated internally.

VHDL implementations (stand-alone IPs): Generic Array Extrema Units VHDL IPs

Report on Parameterized Array Extrema Units: (pdf)

Parameterized Adder/Subtractor with carry in:

The following custom adder/subtractor core is a fully parameterized architecture.

VHDL implementations (stand-alone IPs): Generic Adder/Subtractor wtih carry in VHDL IP

Report on Parameterized Adder/Subtractor with carry in: (pdf)

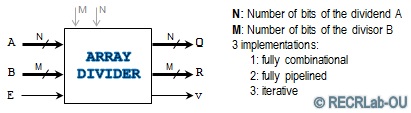

Parameterized Unsigned Integer Divider:

The following custom divider core (for unsigned integers) is a fully parameterized architecture. Three versions are presented: one fully parallel for maximum performance, one fully combinatorial, and one iterative for minimum resources.

VHDL implementations (stand-alone IPs): Generic Divider VHDL IPs

Report on Parameterized divider: (pdf)

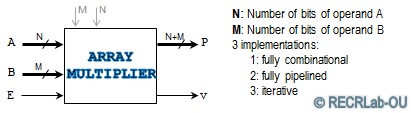

Parameterized Unsigned Integer Multipier:

The following custom multiplier core (for unsigned integers) is a fully parameterized architecture. Three versions are presented: one fully parallel for maximum performance, one fully combinational, and one iterative for minimum resources.

VHDL implementations (stand-alone IPs): Generic Multiplier VHDL IPs

Report on Parameterized multiplier: (pdf)

Parameterized Iterative Signed Multiplier:

The following custom signed multiplier core is a fully parameterized architecture. It is based on the unsigned integer multiplier.

VHDL implementations (stand-alone IP): Generic signed iterative multiplier VHDL IP

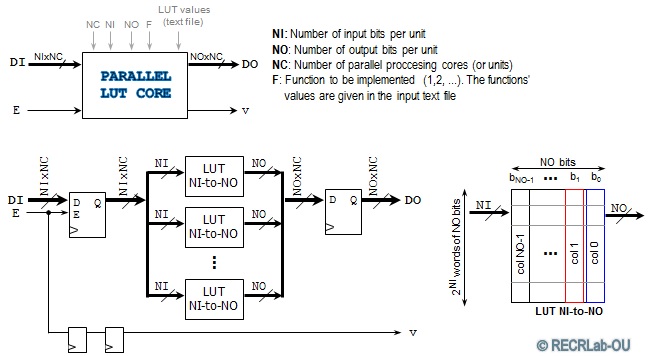

Parameterized Parallel LUT (Look-Up Table) core:

The following custom Parallel LUT core is a fully parameterized architecture.

VHDL implementation (stand-alone IP): Generic Parallel LUT core VHDL IP