SAMPLE INTEGRATED AND PROCESSED CHIPS FOR ECE485/585 Winter 2009

CLASS PROJECTS

Sixteen Bit Floating Point Multiplier

David VanSickle ECE585

Winter 2009

NOTE: THE Science and Engineering Building is on the CHIP…J

=================================================================

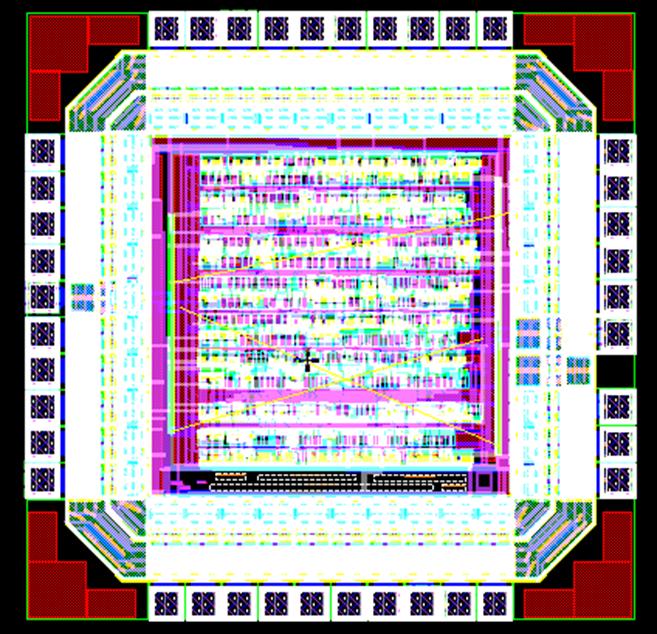

"A Reconfigurable Spiking Neural Network Digital ASIC Simulation and Implementation."

Kevin VanSickle ECE585 Winter 2009

===================================================================================================================================================================

SAMPLING SPIKING NEURAL NETWORK

0.5 CMOS um Technology TINY CHIP è Total area less than 1mm^2

The chip is a Sampling Spiking Neural Network co-processor designed to work in conjunction with a 256K external SRAM memory. It receives an input spike address via an SPI port and then handles the routing of the spike signal among 32,000 synapses and 255 neurons. At the same time, it tracks and records learning statistics. The chip is a highly specialized and optimized specialized linked list processor that manages the connections and routings between neurons and syanpses. It includes a 19 bit address register, a 16 bit data register, a 16 bit list register, a 16 bit adder, and a state machine with 40 states.

================================================================================================