## **Connect Four**

Kyle Johannes

Diana Szeto

James Vankoevering

Kevin Weinert

Final Project Instructor: Daniel Llamocca

### Gameplay

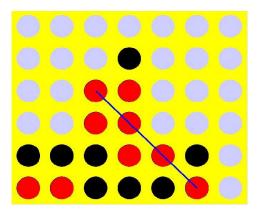

- Connect Four is a classic two-player game.

- The game board has 7 columns and 6 rows, allowing for 42 possible chip slot locations.

- Each player chooses one of two chip colors.

- o In our design, Player 1 is red while Player 2 is black.

- The players take turns dropping one chip into a column at a time.

- The objective of the game is to connect four of your own chips in a row before your opponent.

- The winning four-in-a-row can be vertical, horizontal, or diagonal.

- When a player wins, the board is cleared before beginning the next round.

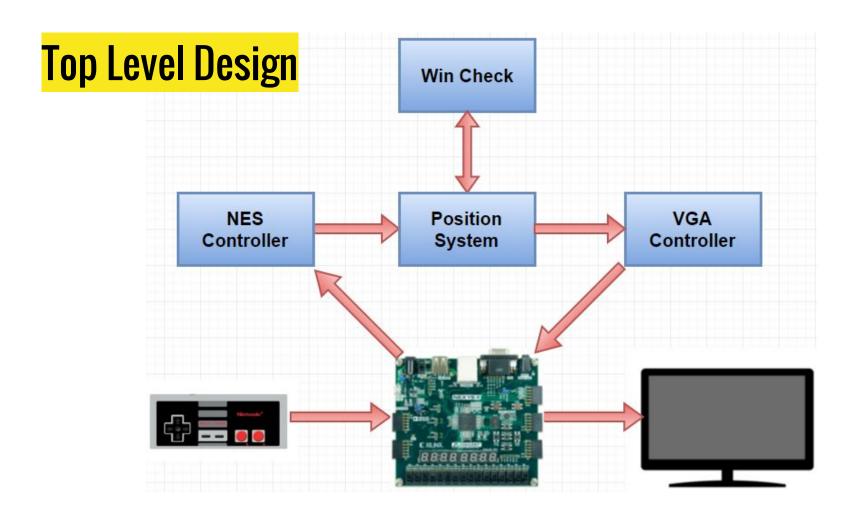

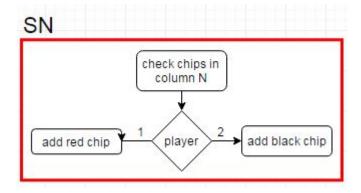

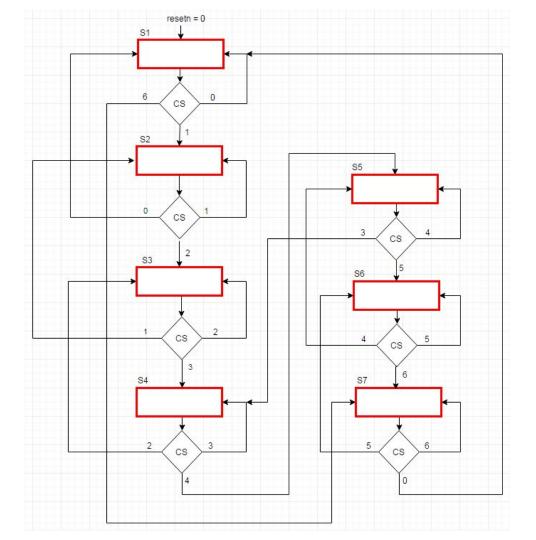

## **Position System**

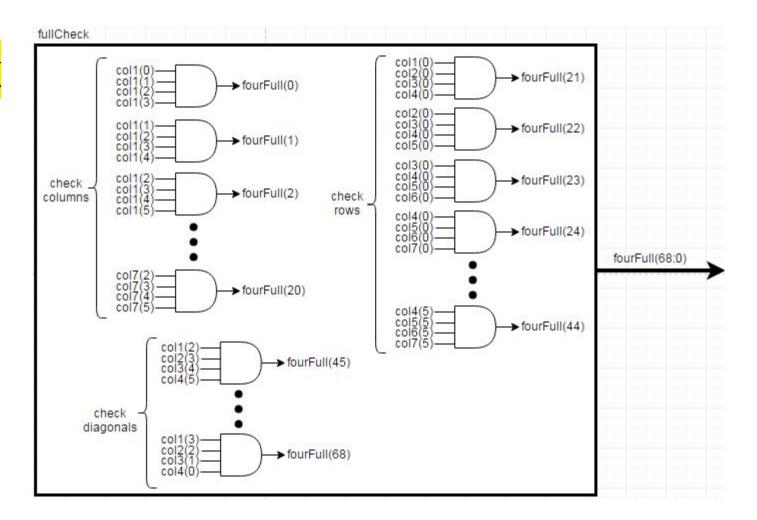

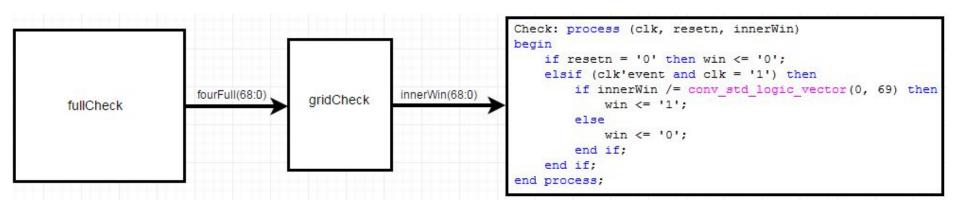

- The Win Check system is made of three main components.

- fullCheck.vhd checks if four adjacent slots in the board are occupied. Outputs a signal that specifies which combinations of four adjacent slots are occupied.

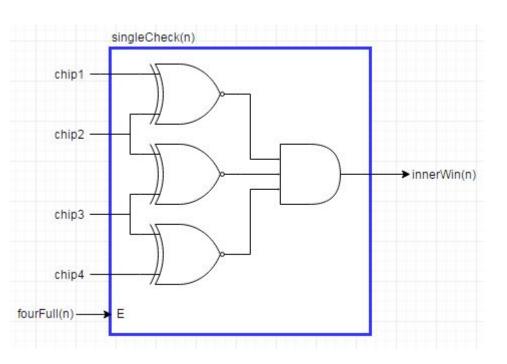

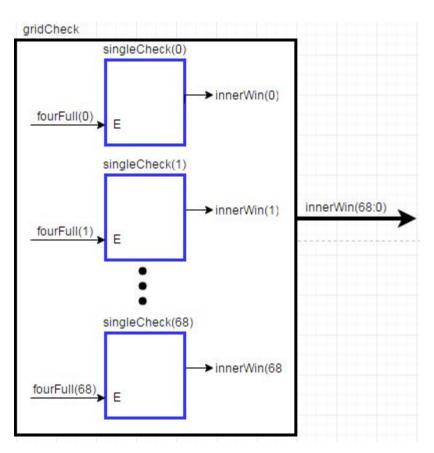

- gridCheck.vhd checks if any four adjacent slots in the board are occupied by the same players chip. Uses singleCheck.vhd to accomplish this. Takes input from the fullCheck.vhd as an enable for the singleCheck.vhd. Outputs a win signal if a player has won, by combining win signals from singleCheck.vhd components.

- singleCheck.vhd checks if the four specified input chips are of the same color. Enabled if four adjacent slots are occupied, the chips in those slots are input. Outputs a win signal if the four chips are the same color.

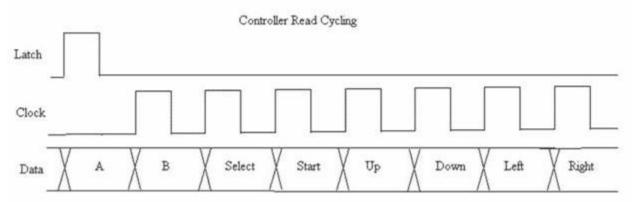

#### **NES Controller**

#### Hardware:

CD4021 parallel to serial shift register

- -buttons are pull-downs, register reads button state on latch

- -shifts data out serially

- 3 data lines: latch, clock, and data out

- Latch loads parallel data in

Image source: http://seb.riot.org/nescontr/

#### **NES Controller**

#### VHDL:

- Clock divider

- Controller clock runs at 400 Hz, divided from 100MHz system clock

- Shift register

- Receives serial data and reassembles as parallel

- Output register

- Once data is shifted completely, the parallel output is stored in an output register until needed

- Timing state machine

- Controller latch timing, output register latching

- "Button press" state machine

- Looks for signal transitions, outputs based on button being pressed and released

### **NES Controller**

Diagram:

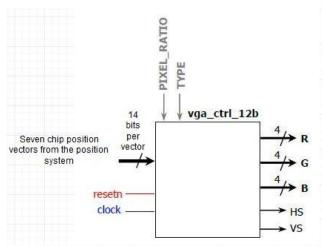

#### **VGA Controller**

- VGA screen used to display game board to players.

- VGA controller and state machine code from Professor Llamocca was used.

- A circuit was added to choose the color to display based on the values of HC and VC.

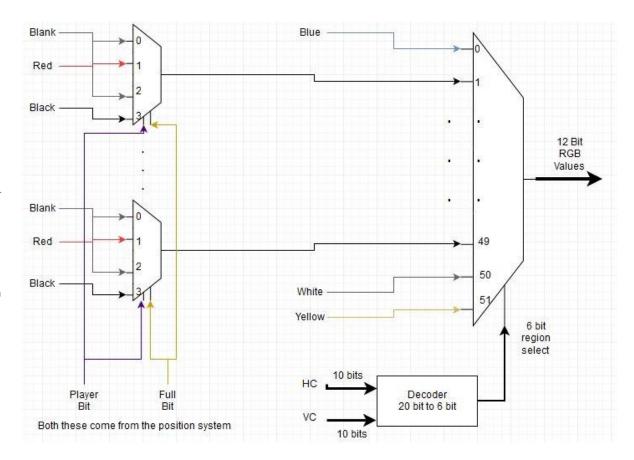

- That circuit used a decoder and multiple MUX to select the input for a particular region on the screen.

- Colors of the chips, whether Red, Black, or Blank were also chosen by a smaller MUX.

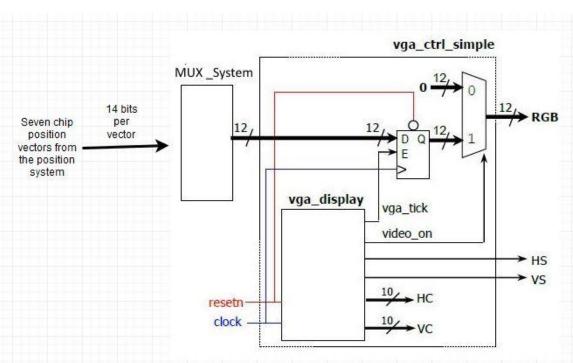

#### **VGA Controller**

Top level of VGA controller

Internal circuits of the VGA controller

#### **VGA Controller**

Multiplexer system designed to determine which color the VGA needs to display based on the region of the display. Color names shown were encoded as standard logic vectors in the VHDL code. The blank chip space color was white.

#### **Gameplay Pictures**

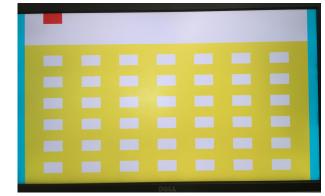

1.

Game start.

Player 1's turn.

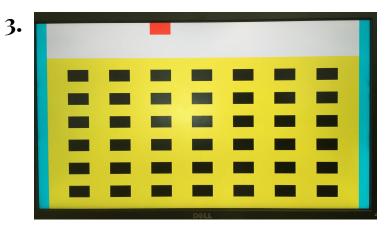

2.

A few turns...

Player 2 wins!

# Wanna Play?