# OAKLAND

# **Course Information**

| INSTRUCTOR   | Daniel Llamocca                                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTACT INFO | email: <u>llamocca@oakland.edu</u>                                                                                                                                    |

| OFFICE HOURS | Tuesday 1:00 to 3:00 pm @ Room EC-438, or by appointment Virtual Office hours also available (Moodle $\rightarrow$ Virtual Office hours via Zoom)                     |

| LECTURES     | Monday/Tuesday/Thursday 5:30 pm - 7:35 pm (CRN: 32012)<br>In-Person Sessions: Tuesday 5:30 – 7:35 pm @ Room DH-136B.<br>Online Sessions (Zoom): Mondays and Thursdays |

| LABORATORY   | See schedule                                                                                                                                                          |

### COURSE CATALOG DESCRIPTION: ECE 5736 - RECONFIGURABLE COMPUTING (4 CREDITS)

Analysis and design of reconfigurable computer architectures. Advanced topics in computer arithmetic. Hardware/Software codesign using Programmable System-on-Chip (ARM processor + FPGA fabric). Introduction to Self-Reconfigurable Architectures. With laboratory and design project. Offered: Summer I. Prerequisite(s): ECE5710.

# COURSE MATERIALS

- The course material will be hosted on Moodle (<u>moodle.oakland.edu</u>). Grades will be periodically posted via this system.

- As a backup resource, the material will also be posted at: www.secs.oakland.edu/~llamocca/Summer2022\_ece5736.html

- Embedded System Design for Zynq PSoC: <u>www.secs.oakland.edu/~llamocca/EmbSysZynq.html</u>

## Техтвоок

• There is no required textbook. Students are encouraged to use the extra references.

### EXTRA REFERENCES:

- Louise H. Crockett, Ross A. Elliot, Martin A. Enderwitz, Robert W. Stewart, *The Zynq Book: Embedded Processing with the ARM® Cortex®-A9 on the Xilinx® Zynq®-7000 All Programmable SoC*, 1<sup>st</sup> ed., 2014.

✓ Free download: <u>http://www.zynqbook.com</u>

- Louise H. Crockett, Ross A. Elliot, Martin A. Enderwitz, Robert W. Stewart, *The Zynq Book Tutorials*, v 1.2, 2014.

✓ Free download (including tutorial files): <u>http://www.zynqbook.com</u>

- VHDL for FPGAs Tutorial: www.secs.oakland.edu/~llamocca/VHDLforFPGAs.html

- Peter J. Ashenden, The Designer's Guide to VHDL, 3<sup>rd</sup> ed., Elsevier, 2008.

- S. Brown, Z. Vranesic, Fundamentals of Digital Logic with VHDL Design, 3rd ed., McGraw Hill, 2009

- B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs, 2<sup>nd</sup> ed., Oxford University Press, Inc., 2009.

## COURSE OBJECTIVES

- 1. Design custom architectures using fixed-point and floating-point arithmetic

- 2. Describe how to unfold a sequential algorithm to turn it into a fully pipelined architecture.

- 3. Learn advanced coding and testbench techniques in Hardware Description Language.

- 4. Design an embedded system using FPGA fabric and an embedded  $\ensuremath{\mathsf{ARM}}\xspace{\ensuremath{\mathbb{R}}}\xspace{\ensuremath{\mathsf{microprocessor}}\xspace}.$

- 5. Describe the process of Dynamic Partial Reconfiguration on an All-Programmable System-on-Chip device.

- 6. Design high-performance application-specific reconfigurable systems.

- 7. Work in a team environment to design a reconfigurable system and communicate the results in a written report and an oral presentation.

# GRADING SCHEME:

| Homeworks:         20%         Laboratory:         50%         Final Project:         30% (June 23 <sup>rd</sup> , 5:30 – 7:35 pm) |

|------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------|

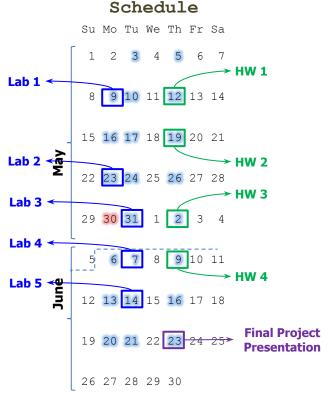

- Homeworks: Homework assignments are meant to strengthen your conceptual understanding of the topics. Completing homework assignments is a key component of this course as it will help students master the course material and prepare them for the examinations. Homeworks will be posted according to the schedule (green rectangles). Students have one week to turn in the completed according to the schedule are NOT

- completed assignments in class. <u>Late submissions are NOT</u> accepted.

- **Laboratory:** This important component of the class will reinforce your understanding of the topics. There will be five (5) labs throughout the semester.

Lab assignments will be posted according to the schedule (blue rectangles). Students have one week to complete the lab assignments and have them checked off by the instructor.

• **Final Project:** Students will work in groups in a Final Project. Each group will prepare an oral presentation and submit a final report.

#### **GRADE ASSIGNMENT:**

| 96-100       | А  | 4.0 |

|--------------|----|-----|

| 90-95        | A- | 3.7 |

| 85-89        | B+ | 3.3 |

| 80-84        | В  | 3.0 |

| 72-79        | B- | 2.7 |

| 66-71        | C+ | 2.3 |

| 60-65        | С  | 2.0 |

| 56-59        | C- | 1.7 |

| 53-55        | D+ | 1.3 |

| 50-52        | D  | 1.0 |

| 49 and below | F  | 0.0 |

# LABORATORY MATERIALS

#### Hardware:

- ✓ Zybo Z7 Board Select the Zybo Z7-10 option To order the board: <u>https://store.digilentinc.com/zybo-z7-zynq-7000-arm-fpga-soc-development-board/</u> Select the Academic Version (~\$150.00).

- ✓ Any other Zynq-7000 board will work as well, e.g.: ZYBO board, ZED Board.

#### Software (free):

- ✓ Preferred: Vivado HL <u>Webpack</u> Edition 2019.1 with SDK and Partial Reconfiguration Feature. To download: <u>https://www.xilinx.com/products/design-tools/vivado/vivado-webpack.html</u> Go to Downloads → Vivado Archive → 2019.1 → Vivado Design Suite - HLx Editions → 2019.1 Full Product Installation

- ✓ Vivado HL <u>Webpack</u> Edition 2020.1 with Vitis (<u>limited support in class</u>) and Partial Reconfiguration Feature. To download: <u>https://www.xilinx.com/products/design-tools/vivado/vivado-webpack.html</u> Go to Downloads → Vivado Archive → 2020.1 → Vivado Design Suite - HLx Editions → 2020.1 Full Product Installation

- ✓ MATLAB® or Octave (open-source version of MATLAB)

## **OUTLINE OF TOPICS**

| Computer Arithmetic                                      | <ul> <li>Unsigned and signed integer numbers: binary representation</li> <li>Fixed-point (FX) arithmetic: addition/subtraction, multiplication, division</li> <li>Floating-point (FP) arithmetic: addition/subtraction, multiplication, division</li> <li>Dual fixed-point (DFX) arithmetic: addition/subtraction, multiplication</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Digital System Design                                    | ✓ Algorithm                                                                                                                                                                                                                                                                                                                                  | <ul> <li>Datapath circuit, Control circuit.</li> <li>ic State Machine (ASM) Charts</li> <li>amples: Bit counting circuit, 7-segment serializer, Serial Multiplier.</li> <li>ams</li> <li>Structural description: hierarchical design (port-map, for-generate).</li> <li>Use of common parametric components: counter, register, shift-register</li> <li>ASM description</li> <li>Testbench generation</li> </ul>                    |  |  |

| Special-Purpose<br>Arithmetic Circuits<br>and Techniques | <ul> <li>CORDIC Algo</li> <li>Square Root</li> <li>LUT approact</li> </ul>                                                                                                                                                                                                                                                                   | nits for fixed-point, floating-point and dual fixed-point.<br>prithm: circular, linear, and hyperbolic. Special functions: exp, ln, sqrt<br>: Iterative version<br>ch: Pixel processor example (gamma correction, contrast stretching)<br>Arithmetic: FIR Filter, DCT<br>Custom-defined datatypes, arrays, packages, functions<br>Parameterization: for-generate, if-generate<br>Embedding counters and registers into ASM diagrams |  |  |

| Pipelining and<br>unfolding                              | <ul> <li>Iterative, array, and pipelined array design</li> <li>Multi-operand addition: iterative (accumulator) vs. pipelined array (adder tree)</li> <li>Multiplier and Divider: iterative vs. pipelined array</li> <li>CORDIC: iterative vs. pipelined array</li> </ul>                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Embedded System in<br>a SoC                              | Hardware       Zynq architecture: FPGA fabric + ARM® microprocessor         Hardware       AXI bus: AXI4, AXI4-Lite, and AXI4-Stream Interfaces         Interface development for AXI4         Software       Introduction to SDK         ARM processor         SD card         Hardware/software co-design                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Dynamic Partial<br>Reconfiguration                       | <ul> <li>Static vs dyna</li> <li>DPR requirem</li> <li>Time and me</li> <li>Dynamic Free</li> <li>JTAG-based r</li> <li>Case example</li> <li>✓ 4-bit LED</li> <li>✓ Pixel proc</li> </ul>                                                                                                                                                   | to Self-Reconfigurable Systems<br>amic reconfiguration.<br>hents: reconfiguration controller, generating and downloading bitstreams.<br>mory overhead<br>juency Control<br>econfiguration and PCAP-based reconfiguration.<br>es:<br>pattern controller (1 RP and 2 RPs).                                                                                                                                                            |  |  |

| Applications                                             | <ul> <li>Dynamic Circi</li> <li>Dynamic Arith</li> <li>Image proces</li> <li>DSP: Audio fi</li> </ul>                                                                                                                                                                                                                                        | ular CORDIC.<br>Imetic: Dynamic Dual Fixed Point Adder/Subtractor.<br>Ising: Dynamic Pixel Processor, 2D FIR Filter<br>Iter<br>Iter                                                                                                                                                                                                                                                                                                 |  |  |

# OUTLINE OF COURSE TOPICS, ASSOCIATED ASSIGNMENTS AND REFERENCE MATERIAL TOPICS SHADED IN GRAY: IN-PERSON LECTURES, OLD ZOOM RECORDINGS AVAILABLE TOPICS SHADED IN RED: ASYNCHRONOUS LECTURES (PANOPTO)

| Week |       | Unit   | Торіс                                                                                                                                                                                   | Associated Material                                                                 | Assignments  |

|------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------|

| 1    | 05/03 |        | Class policies, class structure                                                                                                                                                         | Syllabus                                                                            |              |

|      |       |        | Unit 2, Unit 5: Quick Overview<br>Bit Counting circuit: timing diagram                                                                                                                  | Zynq Book                                                                           |              |

|      | 05/05 | 2      | Bit Counting circuit (n=8): VHDL coding<br>Serial Multiplier 4x4: VHDL coding                                                                                                           | Lecture Notes – Unit 2                                                              |              |

|      |       |        | Experiment: Serial Multiplier 2x2 (ZYBO)                                                                                                                                                | Emb. Sys. on PSoCs Tutorial # 1                                                     |              |

| C    | 05/09 | 5      | Experiment: Introduction to Hardware/Software Design (ZYBO Z7-10)                                                                                                                       | Zynq Book Tutorials (1. First<br>Design on Zynq)<br>Emb. Sys. on PSoCs Tutorial # 2 | Laboratory 1 |

| 2    |       | 2      | Experiment: Serial Multiplier 2x2: (ZYBO Z7-10)                                                                                                                                         | Zynq Book                                                                           |              |

| -    | 05/10 | 5      | Intro to Zynq PS/PL. AXI Timing Diagrams. Overview                                                                                                                                      | Lecture Notes – Unit 5                                                              |              |

|      |       |        | Final Project Guidelines                                                                                                                                                                |                                                                                     |              |

|      | 05/12 | 5      | AXI Timing Diagrams.<br>AXI Lite examples: pixel processor, seq. divider, pip.divider, 2D convolver                                                                                     | Lecture Notes – Unit 5                                                              | Homework 1   |

|      | 05/16 | 5      | Experiment: AXI Lite Custom Peripheral: pixel processor (ZYBO Z7-10)<br>Experiment: AXI Lite Custom Peripheral: 2D convolver (ZYBO Z7-10)                                               | Zynq Book Tutorials (4. IP<br>Creation)<br>Emb. Sys. on PSoCs Tutorial # 3          |              |

|      |       | 1      | Fixed-Point (FX) Arithmetic: examples                                                                                                                                                   | Lecture Notes – Unit 1                                                              |              |

| 3    |       | 3      | CORDIC                                                                                                                                                                                  | Lecture Notes – Unit 3                                                              |              |

| 0    | 05/17 | 5      | AXI Lite: pipelined divider<br>Experiment: AXI Lite pipelined divider (ZYBO Z7-10)<br>AXI Lite: CORDIC circuit                                                                          | Lecture Notes – Unit 5<br>Emb. Sys. on PSoCs Tutorial # 3                           |              |

|      | 05/19 | 5      | AXI Full examples: pixel processor, pip. Divider, 2D convolver                                                                                                                          | Lecture Notes – Unit 5                                                              | Homework 2   |

|      | 05/23 | 5      | Experiment: AXI Full: pixel processor (ZYBO Z7-10)<br>Experiment: AXI Full: convolver 2D (ZYBO Z7-10)                                                                                   | Emb. Sys. on PSoCs Tutorial # 4                                                     | Laboratory 2 |

| 4    | 05/24 | 5      | AXI Full: pipelined divider<br>Experiment: AXI Full pipelined divider (ZYBO Z7-10)<br>AXI Full: CORDIC circuit                                                                          | Lecture Notes – Unit 5<br>Emb. Sys. on PSoCs Tutorial # 4                           |              |

|      | 05/26 | 5      | Experiment: SD Card and AXI4-Full Pixel Processor                                                                                                                                       | Emb. Sys. on PSoCs Tutorial # 5                                                     |              |

|      | 05/31 | 4      | Pipelining: examples                                                                                                                                                                    | Lecture Notes – Unit 4                                                              |              |

| 5    |       | 6      | DPR explanation: JTAG-based, PS+PL, TCL-based flow<br>Pixel processor and DCT circuits. File Organization                                                                               | Lecture Notes – Unit 6                                                              | Laboratory 3 |

|      | 06/02 | 6      | DPR Intro. Design Steps. Tcl-based design flow. File organization for<br>hardware-only project and PS+PL project.<br>Experiment: DPR – Only PL using JTAG: 4-bit LED Pattern Controller | Lecture Notes – Unit 6<br>Emb. Sys. on PSoCs Tutorial # 6                           | Homework 3   |

|      | 06/06 | 6      | Experiment: DPR – PS+PL using PCAP: on Pixel processor<br>Experiment: DPR – PS+PL using PCAP: on DCT                                                                                    | Lecture Notes – Unit 6<br>Emb. Sys. on PSoCs Tutorial # 7                           |              |

| 6    | 06/07 | 6<br>1 | DPR: review of pixel processor and DCT designs: circuit, AXI interface<br>DFX, FP: examples                                                                                             | Lecture Notes – Unit 6<br>Lecture Notes – Unit 1                                    | Laboratory 4 |

|      |       | 5      | Direct Memory Access, Interrupts                                                                                                                                                        | Lecture Notes – Unit 5                                                              |              |

|      | 06/09 | 5      | Experiment: DMA                                                                                                                                                                         | Lecture Notes – Unit 5<br>Emb. Sys. on PSoCs Tutorial # 8                           | Homework 4   |

|      | 06/13 | 5      | Experiment: Interrupts: Pixel Processor                                                                                                                                                 | Lecture Notes – Unit 5<br>Emb. Sys. on PSoCs Tutorial # 9                           |              |

| 7    | 06/14 | 3      | DFX Adder/Subtractor                                                                                                                                                                    | Lecture Notes – Unit 3                                                              | Laboratory 5 |

|      | 00/14 | 7      | DPR and Interrupts: DDFX add/sub design                                                                                                                                                 | Lecture Notes – Unit 7                                                              | Lubbruibry 5 |

|      | 06/16 | 7      | Experiment: DPR and CORDIC: Dynamic CORDIC                                                                                                                                              | Lecture Notes – Unit 7                                                              |              |

| 8    | 06/20 | 7      | Experiment: DPR and Interrupt: DDFX add/sub design                                                                                                                                      | Lecture Notes – Unit 7                                                              |              |

|      | 06/23 |        | Final Project - Presentation                                                                                                                                                            |                                                                                     |              |

# CLASS POLICIES

- Assignments (Homeworks, Laboratory): Unless specifically stated otherwise, the homeworks and laboratory work is individual, and students are not allowed to submit their work in groups.

- Academic conduct policy: All members of the academic community at Oakland University are expected to practice and uphold standards of academic integrity and honesty. Academic integrity means representing oneself and one's work honestly. Misrepresentation is cheating since it means students are claiming credit for ideas or work not actually theirs and are thereby seeking a grade that is not actually learned. Academic dishonesty will be dealt with seriously and appropriately. Academic dishonesty includes, but it is not limited to cheating on examinations, plagiarizing the works of others, cheating on lab reports, unauthorized collaboration in assignments, hindering the academic work of other students.

- **Special Considerations**: Students with disabilities who may require special consideration should make an appointment with campus Disability Support Services, 106 North Foundation Hall, phone 248 370-3266. Students should also bring their needs to the attention of the instructor as soon as possible. For academic help, such as study and reading skills, contact the Academic Skills/Tutoring Center, 103 North Foundation Hall, phone 248 370-4215.

- Add/Drops: The university policy will be explicitly followed. It is the student's responsibility to be aware of deadline dates for dropping courses.

- Attendance: It is assumed that the students are aware of and understand the university attendance policy. Attendance is mandatory and maybe monitored. Students are responsible for all material covered in classes that they miss. There will no excuses for being late to exams.

- Athlete Excused Absences: Students shall inform the instructor of dates they will miss class due to an excused absence prior to the date of that anticipated absence. For activities such as athletic competitions whose schedules are known prior to the start of a term, students must provide their instructors during the first week of each term a written schedule showing days they expect to miss classes. For other university excused absences, students must provide the instructor at the earliest possible the dates that they will miss.

- **Special Circumstances:** The instructor should be notified as early as possible regarding any special conditions or circumstances which may affect a student's performance during the course timeframe (e.g., medical emergencies, family circumstances).

- Mental Health Resources: Oakland University is committed to advancing the mental health and well-being of its students. If you or someone you know is feeling overwhelmed, depressed, and/or in need of support, services are available. For help, contact the OU Counseling Center in the Human Health Building at (248) 370-3465 or the SEHS Counseling Center at 250A Pawley Hall, (248) 370-2633, https://oakland.edu/counseling/sehs-cc/. Student resources can also be found at https://www.oakland.edu/deanofstudents/student-health-safety-resources/. For immediate 24/7 services contact Common Ground at https://commongroundhelps.org/#/ via chat or call or text the word "hello" to 1-800-231-1127.

- **Cellphones:** A ringing cellphone going off during a lecture is disruptive to other students as well as the instructor. Students are strongly advised to set their cellphones to vibrate (not ringing) and leave the classroom discretely to answer the phone.