# Reconfigurable Signed Multiplier (2C and SM) on Zynq-7000 PSOC

Andrew Meesseman and Hussein Alawsi ECE 5736: Reconfigurable Computing Professor D. Llamocca Oakland University

#### **Motivation**

- Implement a system that makes use of dynamic partial reconfiguration (DPR) to show the benefits and possibilities with this feature

- Implement a PL to PS interrupt to show the possibilities available with this feature as well

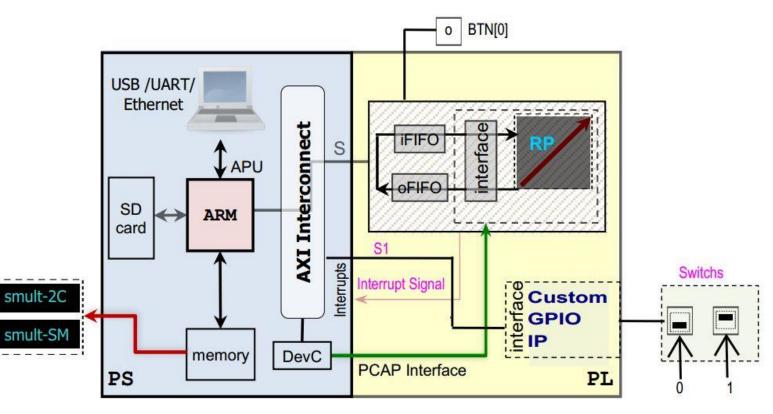

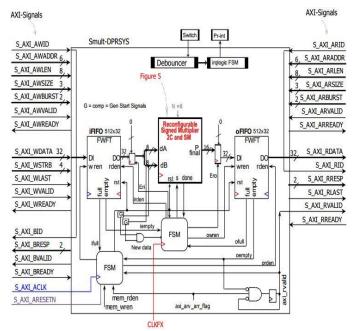

#### High Level PS-PL Interfacing

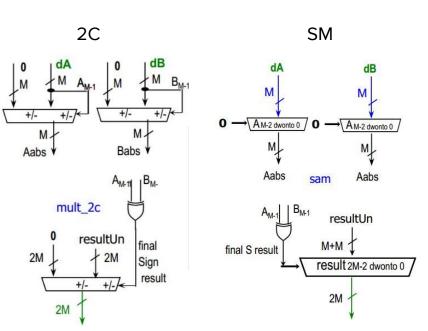

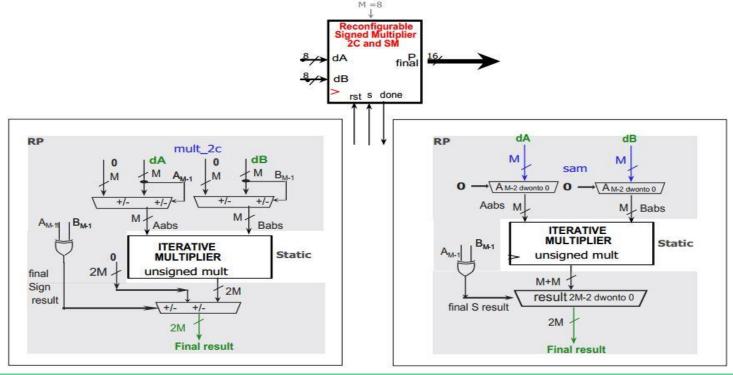

## Signed Multiplier Components

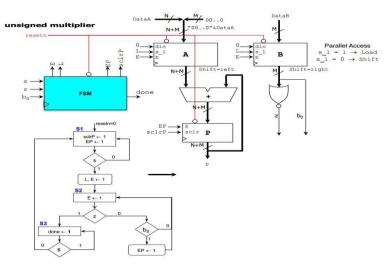

- Unsigned Multiplier

- 2C Logic

- SM Logic

# Static and RP Separation

- Unsigned multiplier is used in both circuits (which is why it is in static)

- All AXI4-Full logic and both FSM's are in the static portion (as they do not change)

# Signed Multiplier Implementation

- AXI4-Full

- Multiplies 8-bit by 8-bit input data and produces a 16-bit output based on the current circuit in the reconfigurable partition (RP)

- Also includes circuit to generate PL to PS interrupt

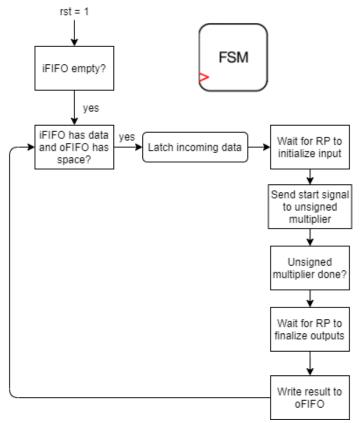

### Signed Multiplier Application FSM

• Controls when input data is sent to circuit and when it is put into oFIFO

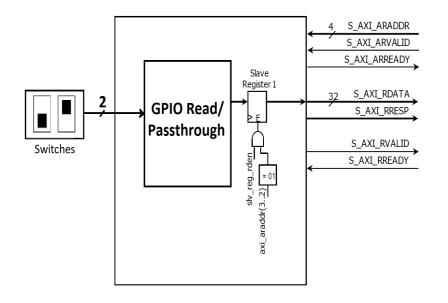

#### **GPIO** Passthrough IP

- AXI4-Lite

- Allows software to determine which bitstream to reconfigure during DPR

### Software Functionality

- Loading partial bitstreams into DDR

- Tx and Rx data from smult IP

- Handling ISR and performing DPR on smult IP

- Includes determining which bitstream to reconfigure by checking switch value

## Simulation Results

| INPUT      | OUTPUT         |                |  |  |  |

|------------|----------------|----------------|--|--|--|

|            | RP mode = "2C" | RP mode = "SM" |  |  |  |

| 0x00000406 | 0x0000018      | 0x0000018      |  |  |  |

| 0x0000FD03 | 0x0000FFF7     | 0x00008177     |  |  |  |

| 0x0000FDFD | 0x0000009      | 0x00003D09     |  |  |  |

| 🐻 s00_axi_awvalid     | 0        |                                                                                                                                                                 |                                                                                               |           |             |                     |            |        |          |  |

|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|-------------|---------------------|------------|--------|----------|--|

| 😽 s00_axi_wdata[31:0] | 00000000 | 00000000                                                                                                                                                        |                                                                                               |           |             | 00000000            |            |        |          |  |

| ₩ ififo_DI[31:0]      | 00000000 | 00000000                                                                                                                                                        |                                                                                               |           |             | 00000000            |            |        |          |  |

| ₩ ififo_DO[31:0]      | 0000fdfd | 00000000 XX 0000fd03 X                                                                                                                                          |                                                                                               |           | 0000 fdfd   |                     |            |        |          |  |

| V ofifo_DI[31:0]      | 00003d09 | 00000                                                                                                                                                           | 1000                                                                                          | X         | 00000018    | 0000018 00008177    |            |        | 00003409 |  |

| V ofifo_DO[31:0]      | 00003d09 | 0                                                                                                                                                               | 0000000                                                                                       | X         | 0000001     | 8 )                 | 00008177   | χ      | 00003409 |  |

| 😽 s00_axi_rdata[31:0] | 00003d09 | 0                                                                                                                                                               | 0000000                                                                                       | X         | 0000001     | 8 X                 | 00008177   | χ      | 00003409 |  |

| 🔓 sig_done            | 0        |                                                                                                                                                                 |                                                                                               |           |             |                     |            |        |          |  |

| 1 <b>8</b> y          | S2       | S1 S2                                                                                                                                                           | <u>)</u><br>(0)<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>() |           | X 85 XC     | <u> </u>            | S5 X S     | e XXXX | S2       |  |

| 6 mode[1:2]           | "SM"     |                                                                                                                                                                 |                                                                                               |           | "51         | 1"                  |            |        |          |  |

| 🖁 s00_axi_awvalid     | 0        |                                                                                                                                                                 |                                                                                               |           |             |                     |            |        |          |  |

|                       | 00000000 | 00000000                                                                                                                                                        |                                                                                               |           |             |                     | 00000000   |        |          |  |

|                       | 00000000 | ^_MI                                                                                                                                                            |                                                                                               |           | 1           | 0000000             |            |        |          |  |

|                       | 0000fdfd |                                                                                                                                                                 |                                                                                               | 0000fdfd  |             |                     |            |        |          |  |

|                       | 0000009  | /\//\///\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\//\///\//\//\///\//\//\///\///\///\///\///\///\///\///\///\///\////// |                                                                                               |           | Λ<br>γ_οι   | 00000018 0000fff7 0 |            |        |          |  |

|                       | 0000009  | 00000000                                                                                                                                                        |                                                                                               |           |             | 00000018            | 0000111    | ·7 χ   | 00000009 |  |

| 😽 s00_axi_rdata[31:0] | 0000009  | 00000000                                                                                                                                                        |                                                                                               |           |             | 00000018            | 0000111    | 7      | 0000009  |  |

| 🖁 sig_done            | 0        |                                                                                                                                                                 |                                                                                               |           |             |                     |            |        |          |  |

| 1 <b>8</b> y          | S2       | S1                                                                                                                                                              |                                                                                               | x sz x0xx | \$5 VOXXXX0 | S5 0 000            | S3 X S5 S6 | XXX    | S2       |  |

| 6 mode[1:2]           | "2C"     |                                                                                                                                                                 |                                                                                               |           | "           | 20"                 |            |        |          |  |

#### Implementation Results

Performs as expected and meets all desired system requirements SD + SMULT Test:

(load\_sd\_to\_memory): Loading 'mult\_sm.bin' to memory (load\_sd\_to\_memory) : File Size: 117448 bytes Close File: Success!

(load\_sd\_to\_memory): Loading 'mult\_2c.bin' to memory (load\_sd\_to\_memory) : File Size: 117448 bytes Close File: Success!

smult\_test (smult\_test) Signed Mult AXI4-Full Peripheral Test Product = 0018 Product = FFF7 Product = 0009

start event loop

(ISR) PL Interrupt occurred! isr done (load\_bit\_to\_pcap) IntrStsReg: F803000F: (load\_bit\_to\_pcap) Interrupt Status bits cleared! IntrStsReg: F803000F (load\_bit\_to\_pcap) DPR: Transfer to start: Source Address: 0011CC78... (load\_bit\_to\_pcap) DPR: Transfer completed!

SMULT\_SM CONFIGURED

-----

Asserting PR\_reset. (smult\_test) Signed Mult AXI4-Full Peripheral Test Product = 0018 Product = 8177 Product = 3D09

#### Demo

# Benefits of Reconfigurable Computing

- Device cost

- Power, energy, and size constraints

- One chip for multiple functionalities

- The RP is capable of hosting however many reconfigurable modules (RM's) and thus many applications

### Conclusions

Partial Reconfiguration along with the abilities of the Zynq-7000 chip and AXI allow for a very advanced system to be created. There are many applications beyond this that could host very advanced circuits (and very advanced RM's). Although the reconfigurable part of this circuit is rather simple, the most important part is showcasing the DPR functionality.

#### References

- 1. <u>https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2019\_1/ug909-vivado-partial-reconfiguration.pdf</u>

- 2. <u>https://www.xilinx.com/support/documentation/sw\_manuals/xilinx2017\_1/ug947-vivado-partial-reconfiguration-tutorial.pdf</u>

- 3. D. Llamocca, "Reconfigurable Computing" Oakland University. 2020.

#### Questions?