#### **Dual Fixed Point Calculator**

ECE 595 Reconfigurable Computing

Instructor:-

Professor Daniel Llamocca

Project by:-

**Andres Jacoby**

Gaurav Agalave

#### Overview

- Motivation

- DFX Adder, Subtractor

- DFX Multiplier

- DFX Divider

- DFX Test bench and verification using Matlab

- Challenges Faced

- Conclusion

#### **Motivation**

- Advantages of DFX

- Less Resources

- Higher precision than FX

- Experience of modelling generic system to enable DPR(Dynamic Partial Reconfiguration)

- Not Widespread

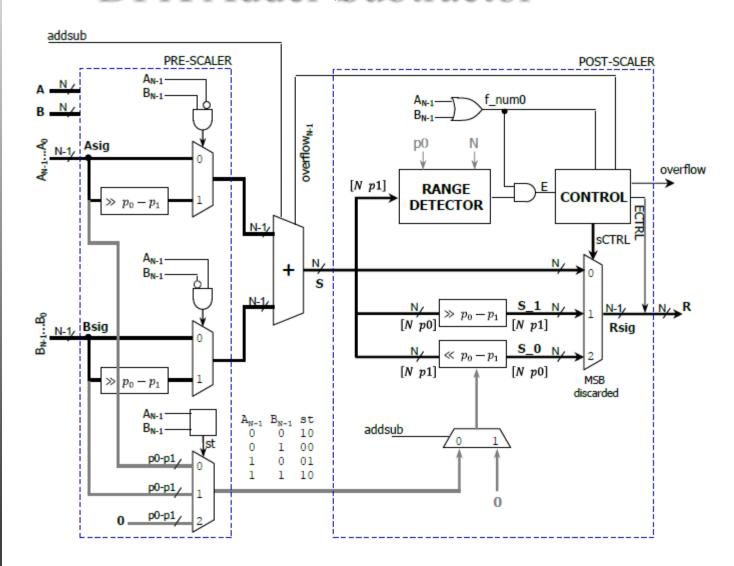

#### **DFX Adder Subtractor**

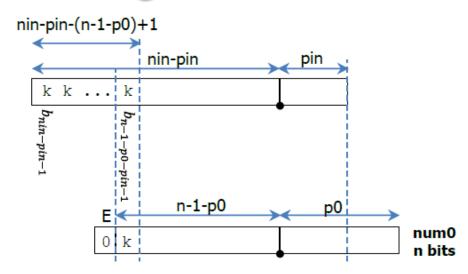

# **DFX Range Detector**

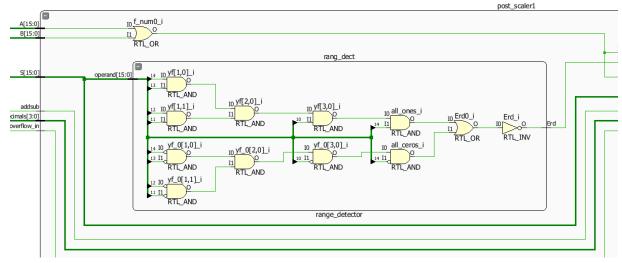

# **DFX Multiplier**

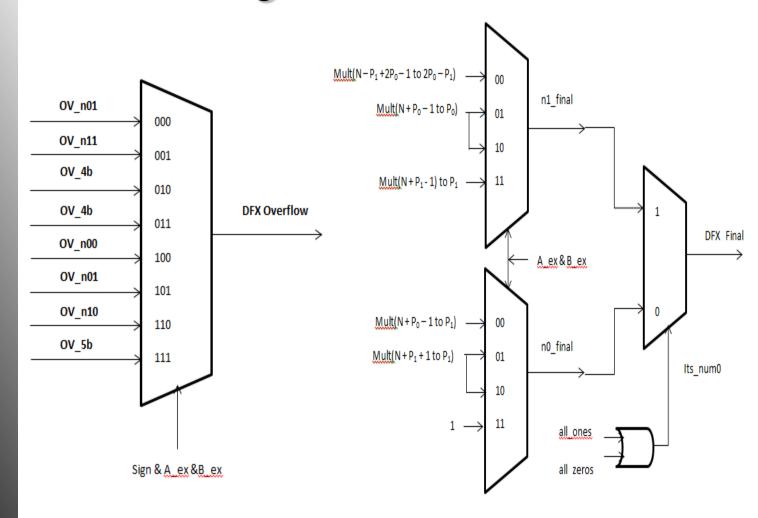

# DFX Multiplier Range Detector & Slicing

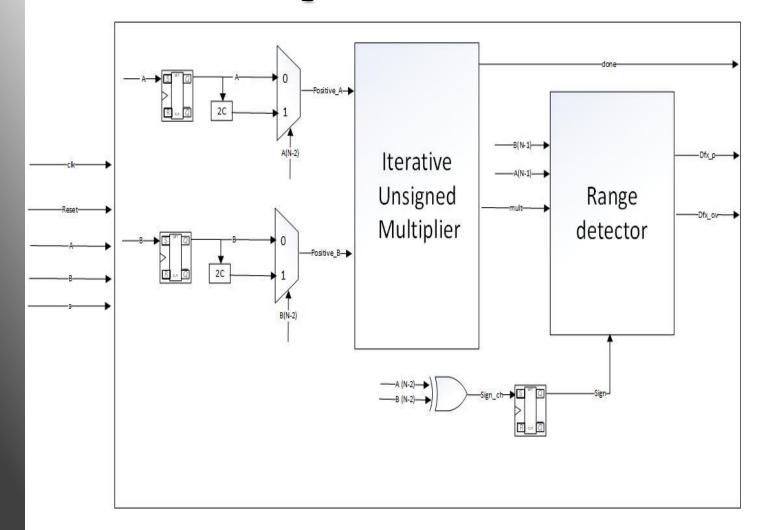

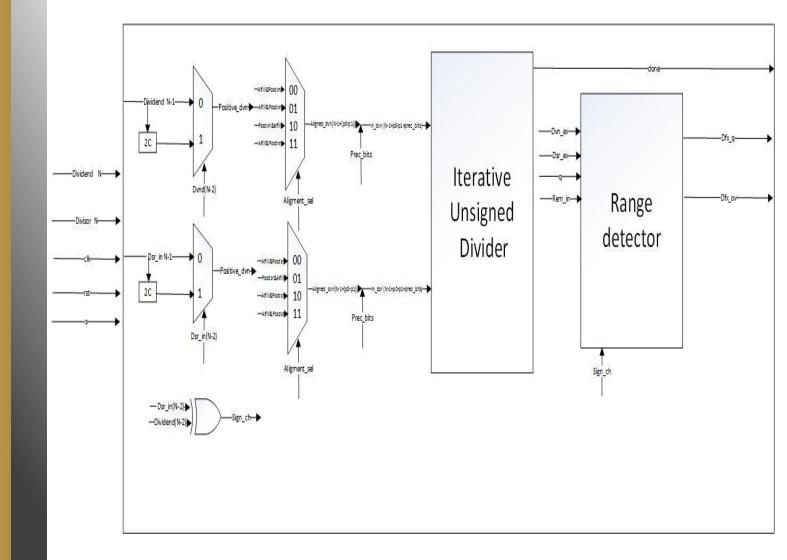

#### **DFX** Divider

#### DFX Divider Range Detector

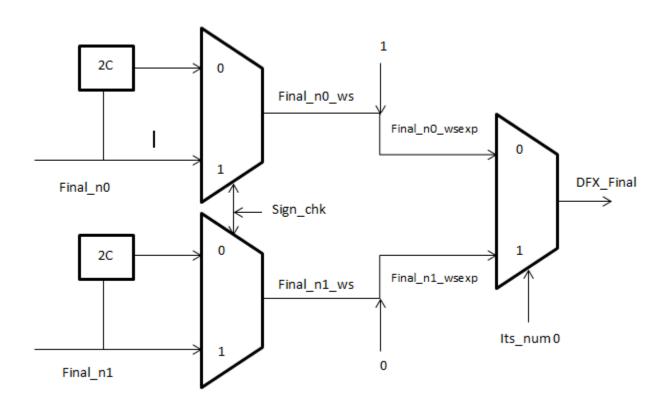

#### **DFX Divider Slicing**

```

fin n0: process(fill z p0x,q)

begin

if (x=p0) then

begin

final n0 \le q(N-2 \text{ downto } 0);

if (x=p1) then

elsif (x>p0) then

if (sign ch='1') then

final n0 \le q((N-p0)+(x-p0)-2 downto abs(x-p0));

dfx ov<=ov neg xp1;

elsif (x<p0) then

final n0 \le q(N-2-abs(p0-x) downto 0) fill z p0x;

dfx ov <= ov pos xp1;

end if:

final n0<=(others=>'1');

end if:

elsif (x>p1) then

if (sign ch='1') then

end process;

dfx ov <= ov neg xgp1;

-- dfx ov<= ov neg xlp1;</p>

fin n1: process(q, fill z p0x)

else

begin

dfx ov <= ov pos xqp1;

if (x=p1) then

end if:

final n1 \le q(N-2 \text{ downto } 0);

elsif (x<p1) then

elsif (x>p1) then

if (sign ch='1') then

final n1 \le q (N + abs(x-p1)-2)

downto abs(x-p1) );

dfx ov<=ov neg xlp1;

elsif (x<p1) then

final n1 \le q (N-2 - (abs(p1-x))) downto 0 ) & fill z p1x;

dfx ov <= ov pos xlp1;

end if:

final n1<=(others=>'1') ;

end if:

end if:

```

end process;

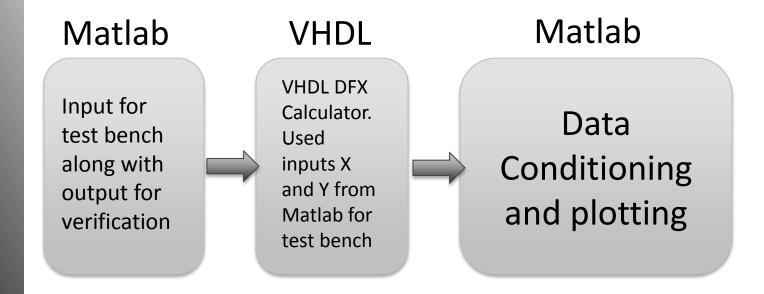

# DFX Calculator in MATLAB(For test bench for VHDL)

- Random floating point number Generated using rand().

- Floating points converted to fixed point format using quantizer based on range.

- E.g.r = quantizer('fixed',[7,5]);q = quantizer('fixed',[7,3]);

- Fixed point numbers again converted into floating point format for calculations.

- Operands along with o/p and overflow data are converted into .txt file.

#### Verification Process Block Diagram

#### Matlab Flow Chart

Random X and Y operands Generation

Generation of text files for both i/p and o/p

Outputs of calculation from Matlab and VHDL

Floating point conversion of both outputs from Matlab and VHDL(DFX formatted)

Plotting of both outputs for comparison of performance and validation.

#### Code Snippet

```

x = 16 * rand([1,100]) - 8; % x random number generator

y = 16 * rand([1,100]) - 8; % y random number generator

n = 8; % Total number of bits

% num0 boundry

b1 = -2^{((n-1)-1)} / 2^5;

b2 = (2^{(n-1)-1} - 1) / 2^5;

% num1 boundry

a1 = -2^{(n-3-2)};

a2 = (2^{(n-3-2)}) - 2^{(-3)};

r = quantizer ('fixed',[7 5]); % num0 fx form

q = quantizer ('fixed',[7 3]); % num1 fx form

- for t = 1:100

if x(t) >= b1 && x(t) <= b2

xfxflbin\{t\} = num2bin(r,x(t)); % num 2 bin for x with num0 fx form

yfxflbin\{t\} = num2bin(r,y(t)); % num 2 bin for y with num0 fx form

else

xfxflbin\{t\} = num2bin(q,x(t)); % num 2 bin for x with num1 fx form

vfxflbin\{t\} = num2bin(q,v(t)); % num 2 bin for v with num1 fx form

end

∟end

% Loosing precision for generating DFX like number

% 100X1 Double

xfxfl = cell(1.100);

yfxfl = cell(1,100);

- for o = 1:100

if x(0) >= b1 && x(0) <= b2

xfxfl(o) = bin2num(r,xfxflbin(o));

yfxfl(o) = bin2num(r,yfxflbin(o));

else

xfxfl(o) = bin2num(q,xfxflbin(o));

yfxfl(o) = bin2num(q,yfxflbin(o));

end

-end

```

#### Code Snippet

```

% Coverting char array(100X7) to string(100X1 cell) for VHDL

xfxflbincell = cellstr(xfxflbin);

yfxflbincell = cellstr(yfxflbin);

xfxflbinvhdl = cell(1,100);

vfxflbinvhdl = cell(1,100);

\exists for d = 1:100

if xfxfl{d} >= b1 && xfxfl{d} <=b2

xfxflbinvhdl(d) = strcat('0',xfxflbincell(d));

else

xfxflbinvhdl(d) = strcat('1',xfxflbincell(d));

end

if vfxfl{d} >= b1 && vfxfl{d} <= b2

yfxflbinvhdl(d) = strcat('0',yfxflbincell(d));

yfxflbinvhdl(d) = strcat('1',yfxflbincell(d));

end

% Addition num1 or num0 conversion with overflow flag

\neg for 1 = 1:100

if zfxfladd(1) <= a1 || zfxfladd(1) >= a2

ovadd(1) = 1;

else

ovadd(1) = 0;

end

if zfxfladd(1) >= b1 && zfxfladd(1) <=b2</pre>

zfinadd{1} = num2bin(r,zfxfladd(1));

add{1} = strcat('0',zfinadd{1});

else

zfinadd{l} = num2bin(q,zfxfladd(l));

add{l} = strcat('1',zfinadd{l});

end

end

```

OAKLAND UNIVERSITY.

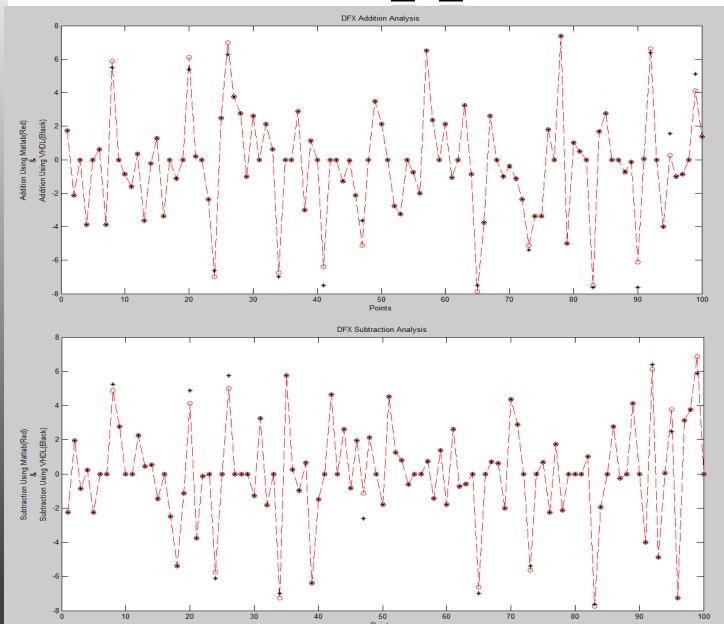

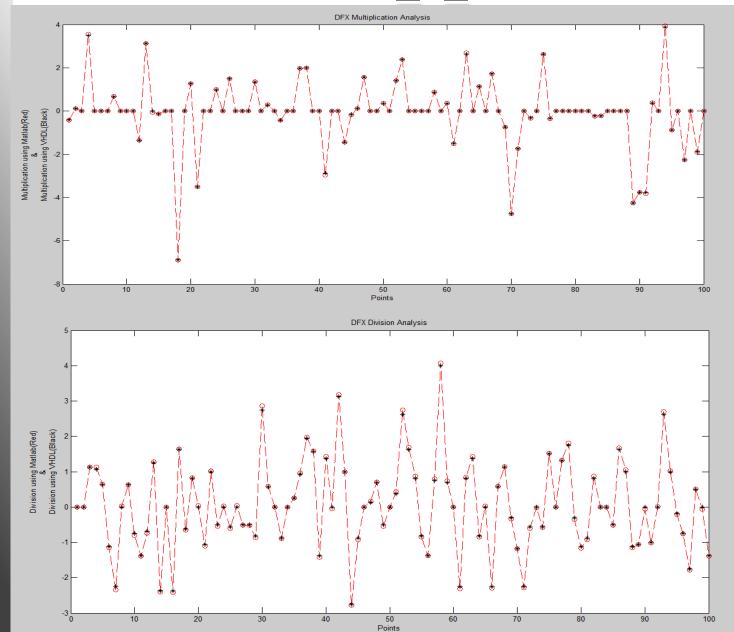

# Plot for DFX 8\_5\_3

# Plot for DFX 8\_5\_3

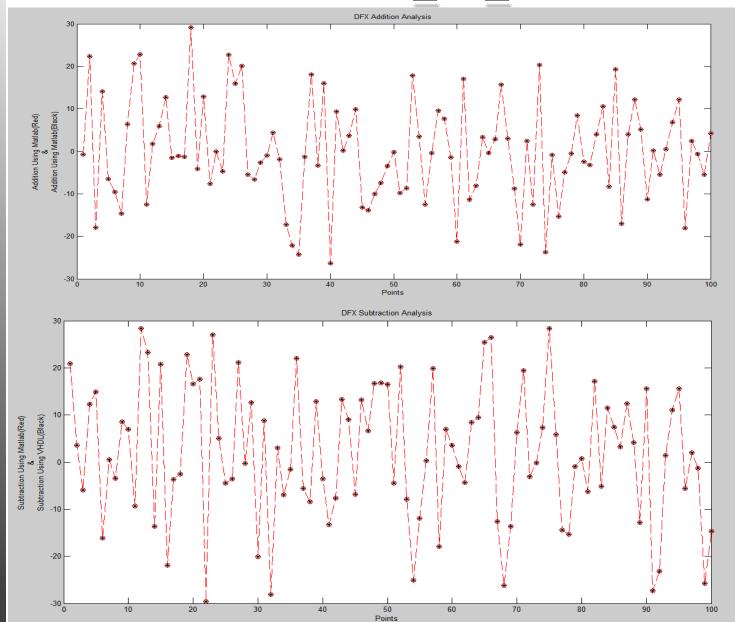

## Plot for DFX 16\_10\_17

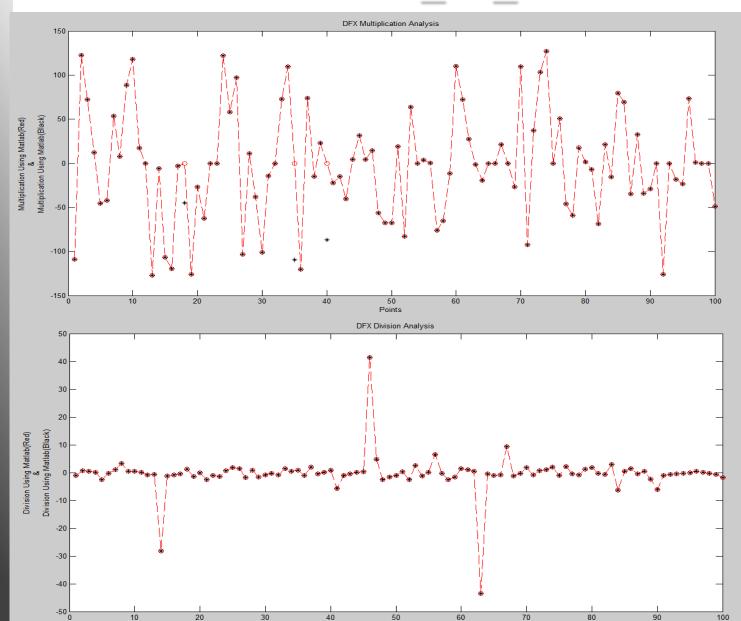

# Plot for DFX 16\_10\_7

Points

# Relative error in both models w.r.t Matlab model.

| Operation      | Relative Error |

|----------------|----------------|

| Addition       | -0.0529        |

| Subtraction    | 1.3037         |

| Multiplication | 0.0198         |

| Division       | -2.9183e-04    |

#### Resources used in VHDL

| LUT used in Operation  | 8_5_3 | 16_10_7 | 24_15_10 | 32_20_15 |

|------------------------|-------|---------|----------|----------|

| Addition & Subtraction | 31    | 64      | 76       | 101      |

| Multiplication         | 73    | 187     | 302      | 353      |

| Division               | 84    | 190     | 346      | 443      |

# Time required for 1 operation in VHDL

| Operation              | Time          |

|------------------------|---------------|

| Addition & Subtraction | Combinational |

| Multiplication 8_5_3   | 8 Clocks      |

| Division<br>8_5_3      | 16 Clock      |

## Challenges Faced

- VHDL

- MATLAB

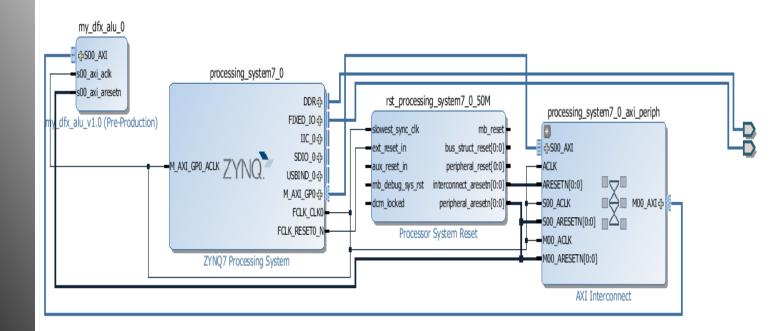

### DFX IP Package

#### DFX Calculator Demo

```

#define DELAY 1000000

DFX ALU BASE

operand_8_addition: u32

/* Define the base memory address of the led controller IP core */

out_add8: u32

#define DFX ALU BASE 0x43C00000 // sometimes the xparameters.h is wrongly created with the wrong

add8: u8

// low address for MYPIX peripheral

// always look at the Address Editor for the correct address

operand8_subtraction : u32

out sub8: u32

⊖ //high part A, low B

sub8 : u8

//sub A-B

ov : u8

/* main function */

operand8_multiplication: u32

u32 operand 8 addition = 0x0000ab04; //A=0xab B=0x04>> expected output 0xAC

u32 out add8=0;

out mul8: u32

u8 add8=0;

mul8: u8

operand8_division: u32

u32 operand8 subtraction = 0x0001bca6; //A(x) - B(y) >> A=0xbc, B=0xa6 >> expected output 0x96

out div8: u32

u32 out sub8=0;

div8 : u8

u8 sub8=0;

u8 ov=0:

main(void): int

u32 operand8 multiplication = 0x00017405; ://14>>A=0x74, B=0x05>> expected output 0x80

u32 out mu18=0;

u8 mul8=0:

u32 operand8 division = 0x0001d6af; //dividend(A=y), Dsr (B=x) >> expected output 0x64

u32 out div8=0;

u8 div8=0;

💠 🗶 🖳 🗀 📗 SDK Log 🛭

🖁 Problems 🔊 Tasks 📮 Console 🗏 Properties 📮 SDK Terminal 🛭

Connected to: Serial ( COM7, 115200, 0, 8)

: Connected to target on host '127.0.0.1' and port '3121'.

16:09:52 INFO : 'targets -set -filter {jtag cable name =~ "Digilent Zybo 2102796554

DFX ALU test begin

16:09:54 INFO : FPGA configured successfully with bitstream "C:/final prj595/projection

16:10:11 INFO : ps7 cortexa9 0 Processor is in use. Please stop existing Run or Del

Input value for addition: 0000AB04

16:10:21 INFO : Processor reset is completed for ps7 cortexa9 0

Output value for Add8: AC

16:16:26 INFO : Connected to target on host '127.0.0.1' and port '3121'.

There is NO overflow in add8!

16:16:27 INFO : 'targets -set -filter {jtag cable name =~ "Digilent Zybo 2102796554

Input value for subtraction: 0001BCA6 Output value for Sub8: 96

16:16:29 INFO : FPGA configured successfully with bitstream "C:/final_prj595/projections."

There is NO overflow in sub8!

16:17:46 INFO : ps7 cortexa9 0 Processor is in use. Please stop existing Run or Del

Input value for multiplication: 00017405 Output value for Mul8: 80

16:17:53 INFO : Processor reset is completed for ps7 cortexa9 0

There is NO overflow in mul8!

16:23:47 INFO : Connected to target on host '127.0.0.1' and port '3121'.

Input value for division: 0001D6AFOutput value for Div8: 64

16:23:48 INFO : 'targets -set -filter {jtag cable name =~ "Digilent Zybo 2102796554

```

Send Clear

There is NO overflow in div8!

End of test.....

Smart Insert

16:27:27 INFO : Processor reset is completed for ps7\_cortexa9\_0

16:24:18 INFO : Processor reset is completed for ps7 cortexa9 0 16:25:17 INFO : Connected to target on host '127.0.0.1' and port '3121'. 16:25:17 INFO : 'targets -set -filter {jtag cable name =~ "Digilent Zybo 2102796554 16:25:20 INFO : FPGA configured successfully with bitstream "C:/final prj595/project 16:27:19 INFO : ps7 cortexa9 0 Processor is in use. Please stop existing Run or Del

16:23:50 INFO : FPGA configured successfully with bitstream "C:/final prj595/projection

16:24:14 INFO : ps7 cortexa9 0 Processor is in use. Please stop existing Run or Del

74:1

# Thank you! Questions?