### Introduction

- Teaches players how to play chess while elevating the overall gaming experience

- Uses real-time piece tracking, intuitively mapping user-selected moves

- Will help guide and teach chess players of any level to learn and understand certain strategies

- Involves two boards to handle separate functions

Dragon12 using HCS12 microprocessor to handle the design

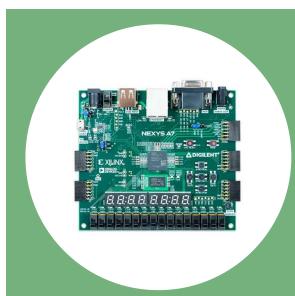

Nexys Artix-7 FPGA to handle the display

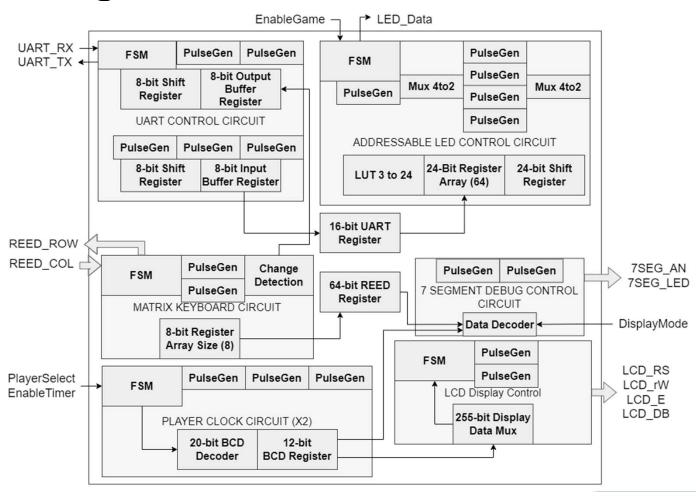

# **Block Diagram**

# Receiving

- The nexys will receive data from the Dragon HCS12 that mimics the structure of a chess board.

- From here the Nexys will be able to display certain things needed on the physical board.

- The Nexys will update the dragon with new data.

```

void main(void) {

startup();

Game_Over = 0;

for(;;) {

CaptureData():

//piece is picked up

if ((temp_reg & piece_mask) == 3){

RookMoves(p,q);

if ((temp_reg & piece_mask)== 4){

QueenMoves(p,q);

if ((temp_reg & piece_mask) == 2){

BishopMoves(p,q);

if ((temp_reg & piece_mask) == 1){

KnightMoves(p,q);

if ((temp_reg & piece_mask)== 5){

KingMoves(p,q);

if ((temp_reg & piece_mask) == 0){

PawnMoves(p,q);

SendData()

//available moves are sent to nexys

MSDelay(100):

UpdateBoardCapture();

//piece is placed, start from the top

Check(c,v);

if(Game_Over == 1){

//play animation celebration forever or until system r

for(k = 0; k < 8; k++){

for(1 =0; 1<8; 1++){

temp_chess_board[k][l] = temp_chess_board[k][l] & red_mask;

f7

g7

h7

a7

d7

b7

c7

e7

K = 1

K = 2

K = 3

K = 5

K = 6

King

Knight

Bishop

Queen

Bishop

Knight

6

a6

b6

c6

d6

e6

f6

g6

f5

g5

h5

5

a5

b5

c5

d5

e5

b4

d4

f4

h4

a4

c4

e4

g4

3

d3

f3

g3

h3

a3

b3

c3

e3

```

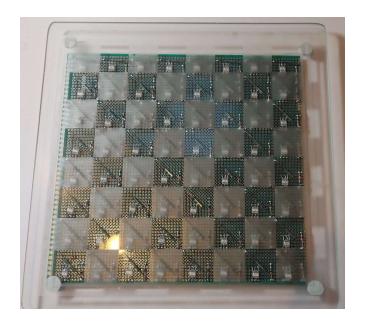

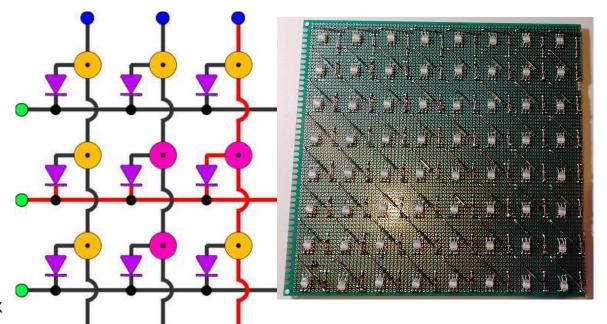

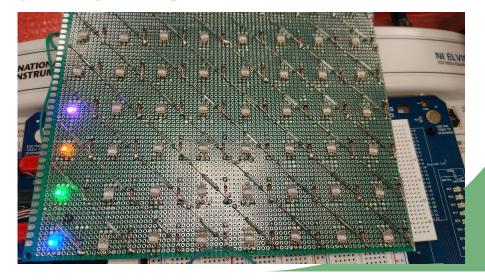

# **Physical Hardware**

- ➤ Dragon HCS12

- ➤ Nexys Artix-7

- ➤ Glass chess board

# Electrical System

### Circuitry Includes:

- ✓ Reed switches

- Magnetic switches

- ✓ Diodes

- To allow multiplexed matrix input data

- ✓ Addressable RGB LED strip

- To address specific squares

### **Functions involved**

LCD\_FSM.vhd

matrixKey\_Top.vhd

Sending, receive, and updating data regarding chess pieces

These functions control all displays revolving around the LED's

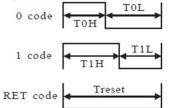

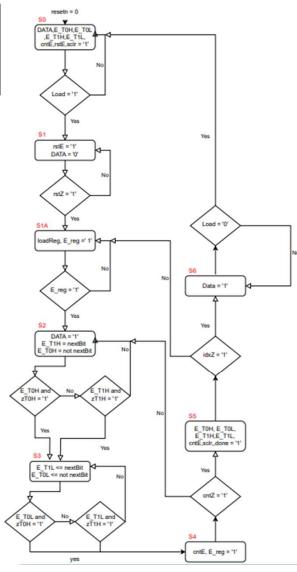

### **LED FSM**

- Components:

- my\_genpulse\_sclr

- my\_pashiftreg

- counterModN

- Outputs:

- y, idxZ, rstZ, nextBit

- Purpose:

- Loops through 24 bits necessary for specific color needed on LED array.

- FSM starts when signal is received from the Dragon Board.

#### Data transfer time( TH+TL=1.25µs±600ns)

| T0H | 0 code ,high voltage time | 0.35us     | ±150ns |

|-----|---------------------------|------------|--------|

| T1H | 1 code ,high voltage time | 0.7us      | ±150ns |

| TOL | 0 code , low voltage time | 0.8us      | ±150ns |

| T1L | 1 code ,low voltage time  | 0.6us      | ±150ns |

| RES | low voltage time          | Above 50µs |        |

#### Sequence chart:

#### Cascade method:

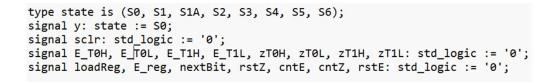

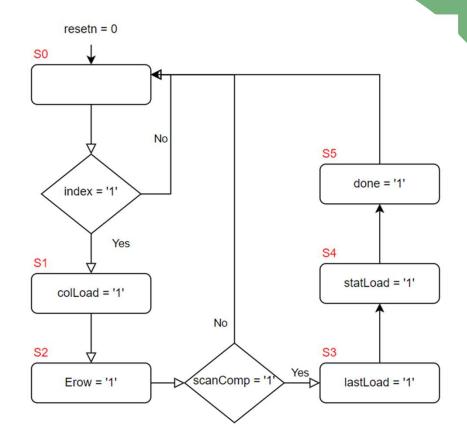

### **MATRIX FSM**

- Outputs:

- Y

- States & Signals

```

type state is (S0, S1, S2, S3, S4, S5);

signal y: state := S0;

```

- Purpose:

- Two counters, one to delay while the other is a row counter.

- Continuous loop. Turns on a column, applies power and reads input row by row.

### **Test Bench**

- Setup to test the vhdl design that we have implemented

- > STIM: a loop involving RXdata that we predefined as a string

```

signal RXdata: std_logic_vector (1 to 44):= "0001110011"&"0000000001"&"1111"&"0001110011"&"0100000001";

ARCHITECTURE behavior OF tbfinal IS

BEGIN

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT FinalTop is

-- Instantiate the Unit Under Test (UUT)

uut: FinalTop PORT MAP (

Port ( clock : in STD LOGIC;

clock => clock,

resetn : in STD LOGIC;

resetn => resetn,

UART_RX : in STD_LOGIC;

UART_RX => UART_RX,

UART_TX : out STD_LOGIC;

UART TX => UART TX,

REED_COL : in STD_LOGIC_VECTOR (7 downto 0);

REED COL => REED COL,

REED_ROW : out STD_LOGIC_VECTOR (7 downto 0);

REED_ROW => REED_ROW,

LED_7seg : out STD_LOGIC_VECTOR (7 downto 0);

LED_7seg => LED_7seg,

AN 7seg => AN_7seg,

AN_7seg : out STD_LOGIC_VECTOR (7 downto 0);

LED data => LED data,

LED data : out STD LOGIC;

LCD RS => LCD RS,

LCD RS : out STD LOGIC;

LCD rW => LCD_rW,

LCD rW : out STD LOGIC;

LCD_E => LCD_E,

LCD E : out STD LOGIC;

LCD DB=> LCD DB

LCD DB : out STD LOGIC VECTOR (7 downto 0));

END COMPONENT;

-- Clock process definitions

clock_process :process

--Inputs

signal UART_RX : std_logic := '1';

clock <= '1'; wait for T/2;

signal REED_COL : std_logic_vector (7 downto 0) := x"01";

clock <= '0'; wait for T/2;

signal resetn : std_logic := '0';

signal clock : std_logic := '0';

-- Stimulus process

stim_proc: process

--Outputs

signal UART TX : std logic;

- hold reset state for 10 ns.

signal REED_ROW : std_logic_vector (7 downto 0);

wait for 15 ns;

signal LED_7seg : std_logic_vector (7 downto 0);

signal AN_7seg : std_logic_vector (7 downto 0);

-- insert stimulus here

signal LED_data : std_logic;

wait for 1 ms;

signal LCD RS : std logic;

for i in 1 to 44 loop

signal LCD_rW : std_logic;

UART RX <= RXdata(i);

signal LCD E : std logic;

wait for 104167 ns;

signal LCD_DB : std_logic_vector (7 downto 0);

end loop;

-- Clock period definitions

wait;

end process:

constant T : time := 10 ns;

```

# **Possible issues**

Code being written by multiple authors

Two boards sending and receiving data

### **Conclusion**

- The project shows how we can implement VHDL skills into a physical project.

- Learned critical problem solving skills when debugging.

- The VHDL side of this project is complete however there are some improvements we would like to make in the future regarding the embedded C data and physical appearance.