### ECE-4710 Final Project

Professor Daniel Llamocca

Submitted by: Connor Goetz Ethan Postma Matthew Hait

# Introduction

- 16-bit machine code, multicycle microprocessor circuit via FPGA implementation

- 31 accessible registers

- 2 utilized for specific purposes

- 1 indexed (Register 1 address 0x01)

- Included program and data memories (using blockRAM)

- Four basic machine code categories

|         | 1                             |       |          |         |                                              |                 |  |  |  |

|---------|-------------------------------|-------|----------|---------|----------------------------------------------|-----------------|--|--|--|

| OP CODE | Offset Bits 7 to 2            |       | Source B | Off     | fset Bits 1 to 0                             | Function        |  |  |  |

| 10      |                               |       |          | -       |                                              |                 |  |  |  |

|         |                               |       | Function |         | Outcome                                      |                 |  |  |  |

|         |                               |       | 00       |         | PC = PC + Offset (Signed)                    |                 |  |  |  |

|         |                               |       | 10       |         | PC = PC + Offset (Signed)                    |                 |  |  |  |

|         |                               |       |          |         | if Source B = 0                              |                 |  |  |  |

|         |                               |       | 11       |         | PC = PC + Offset (Signed                     |                 |  |  |  |

|         |                               |       |          |         | if Source E                                  | 3 < 0           |  |  |  |

|         |                               | 1     | 10       | A = .   | A xor B (Bitwi                               | se)             |  |  |  |

|         |                               |       | 4.4      |         | A                                            |                 |  |  |  |

| OP CODE | Unused                        |       | Source B |         | Stack OP                                     | Function        |  |  |  |

| 10      | <u>X X X X X</u>              |       |          | _       |                                              | 01              |  |  |  |

|         |                               |       | Stack OP |         | Outcome                                      |                 |  |  |  |

|         |                               |       | 00       |         | SP = SP + 1                                  |                 |  |  |  |

|         |                               |       | 01       |         | SP = SP - 1                                  |                 |  |  |  |

|         |                               |       | 10       |         | Store B or                                   | n Stack, SP + 1 |  |  |  |

|         |                               | 11    |          |         | Pull data f                                  | from stack      |  |  |  |

|         |                               |       |          |         | onto B, SP                                   | ° - 1           |  |  |  |

|         | Ļ                             | 0011  |          | R = R - |                                              |                 |  |  |  |

| OP CODE | Signed 14-bit Immediate Value |       |          |         |                                              |                 |  |  |  |

| 11      |                               |       |          |         |                                              |                 |  |  |  |

|         |                               | 1 DIR | <u>N</u> |         | ted by N in DIR Dir<br>, '1' = left (Signed) |                 |  |  |  |

### **Block Overview**

- 4 Basic Blocks:

- Data Path

- Program Counter

- Data Memory

- Serializer

- 2 Finite State Machines

- Program Counter

- Data Path

- Inherent FSM and blockRAM reads cause delays

- Multi-cycle Processor as a result

- User input is machine code .txt file

- Output is displayed on seven segment displays

- Register 30 (Address 0x1E) reserved for output data

Block Overview Data Path

Program Counter 7- Seg Serializer Program

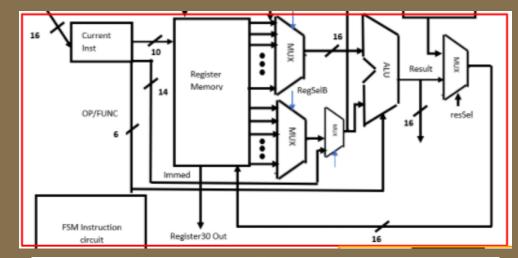

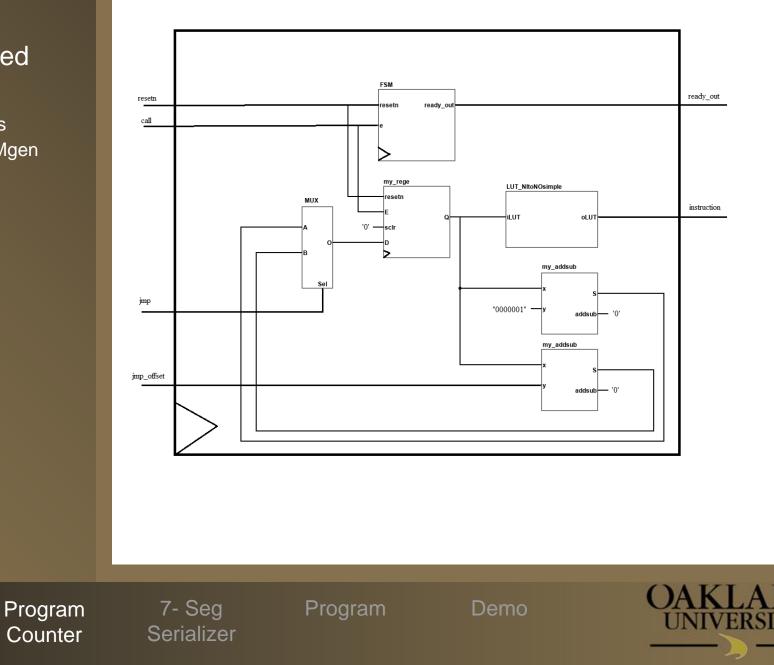

### **Data Path**

Register Memory:

• 31 Registers, my\_rege

#### ALU:

- Takes instructions directly from machine code

- Ability to perform arithmetic, logic, and branch checking operations

- Emits asynchronous "branch\_check" signal based upon current instruction (check for negative or zero)

- Made up of adders, logic statements, and a bit-shifter

- Purely combinatorial circuit, i.e. all possible outcomes calculated each cycle

- Calculations asynchronous at cost of extra hardware

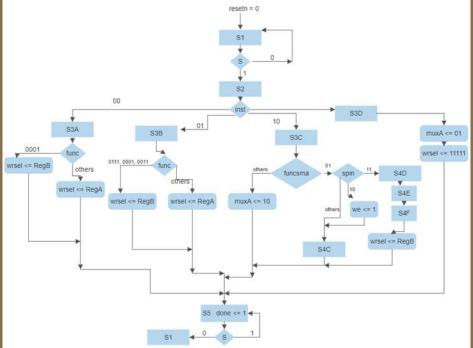

#### Finite State Machine:

- Controls register enables and write signals

- Controls stack data memory signals

- Multicycle, but simplifies instruction decoding

Block Overview Data Path

Program Counter

7- Seg Serializer Program

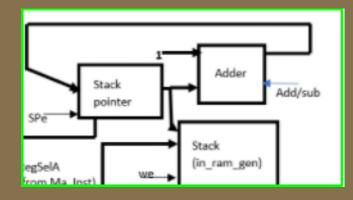

### Data Path - Data Memory

#### • "Stack" like system

- User can pull data, push data, increment or decrement pointer

- Unlike traditional stack, fills top up

- 16-bit width, same as onboard registers

#### • Utilizing the onboard blockRAM

- Creates a time delay as reading takes extra cycles

- Very large space relative to what can be accomplished with a ram emulator

- Shares blockRAM with the program file

- To prevent data overwrites, begins at address 0x2000

| Stack OP | Outcome                  |

|----------|--------------------------|

| 00       | SP = SP + 1              |

| 01       | SP = SP - 1              |

| 10       | Store B on Stack, SP + 1 |

| 11       | Pull data from stack     |

|          | onto B, SP - 1           |

#### --RAM

Block Overview Data Path

Program Counter 7- Seg Serializer Program

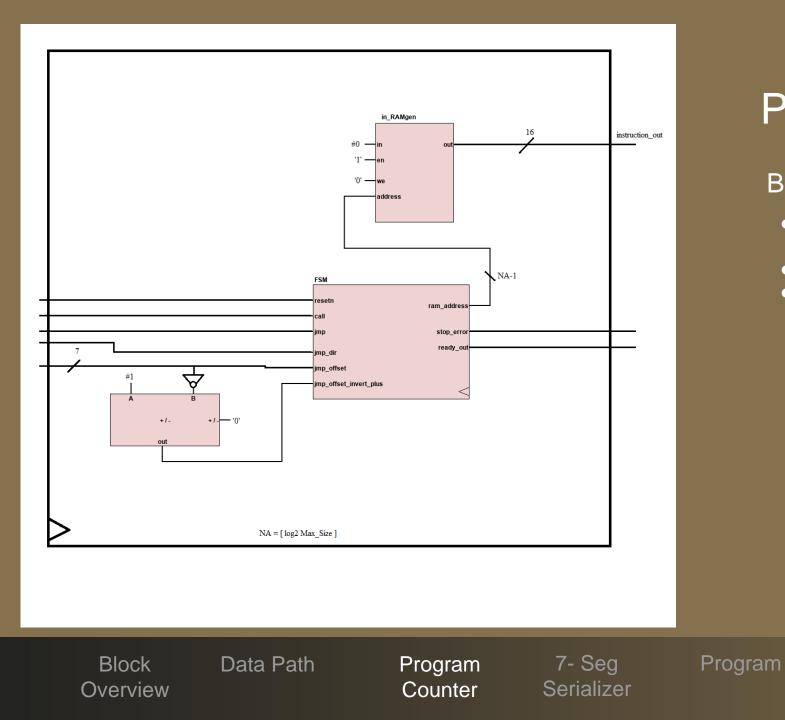

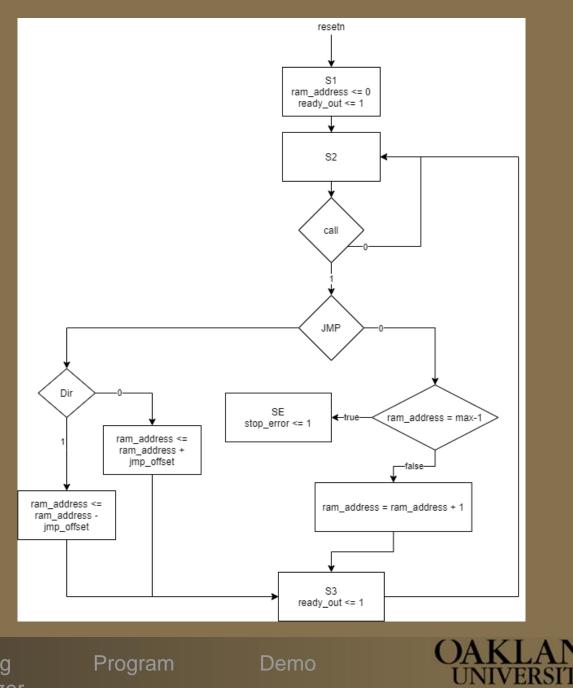

### Program Counter

#### Block Diagram

- "Max\_Size" is number of stored instruction

- Utilizes blockRAM

Demo

- Block *grows* to fit instructions

- Max\_Size changes NA width

- NA affects RAM allocation

- NA affects ram\_address width

OAKLANI UNIVERSITY.

### Program Counter

#### Finite State Machine

- "stop\_error" end of instruction indicator

- S3 initializes processor

Block Overview Data Path

Program Counter 7- Seg Serializer

| Name                     | Value    | 0.000 ns | 200.000 ns | <sup>400.000</sup> r | s اوەن. مە | 0 ns  80 | 0.000 ns     |

|--------------------------|----------|----------|------------|----------------------|------------|----------|--------------|

| le clock                 | 0        |          |            |                      |            |          |              |

| 🐻 resetn                 | 1        |          |            |                      |            |          |              |

| la call                  | 0        |          |            |                      |            |          |              |

| 1a jmp                   | 0        |          |            |                      |            |          |              |

| 诸 jmp_dir                | 0        |          |            |                      |            |          |              |

| la ready_out             | 0        |          |            |                      |            |          |              |

| > 😽 jmp_offset[3:0]      | 8        |          | 0          | X                    |            | 8        |              |

| instruction_out[15:0]    | 0003     | 0000 X   | 0001 X     | 0002 X               | 000a X     | 0002     | <u> 0003</u> |

| ₩т                       | 10000 ps | 10000 ps |            |                      |            |          |              |

| > 😽 RAM_address[11:0]    | 003      | 000 X    | 001        | 002 X                | 00a        | 002      | X 003        |

| > 😼 wev[1:0][3:0]        | 0,0      | 0,0      |            |                      |            |          |              |

| > 😼 sel[0:0]             | 0        |          |            | 0                    |            |          |              |

| 1 <b>⊌</b> y             | S2       | \$2      | \$2<br>    | S2                   | \$2        | \$2      | \$2          |

| > 😼 ram_direct_out[15:0] | 0003     | 0000     | 0001       | 0002 X               | 000a X     | 0002     | X 0003       |

Block Overview Data Path

Program Counter 7- Seg Serializer Program

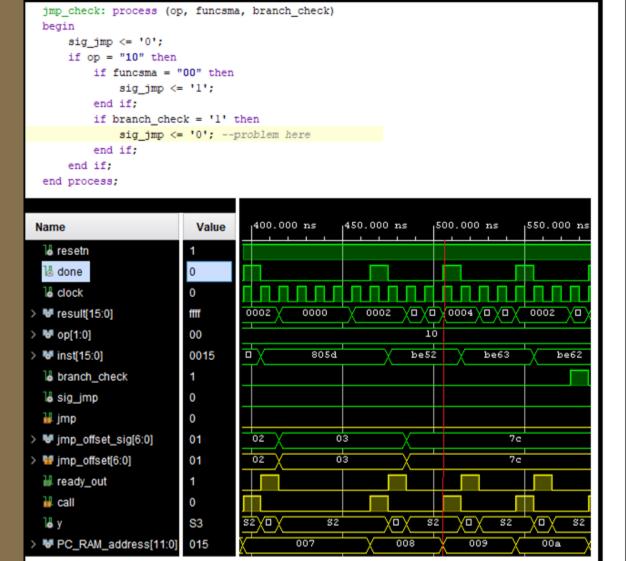

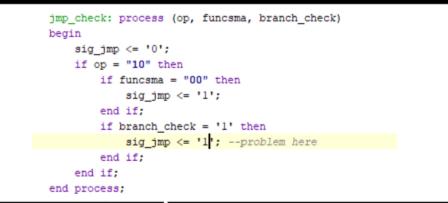

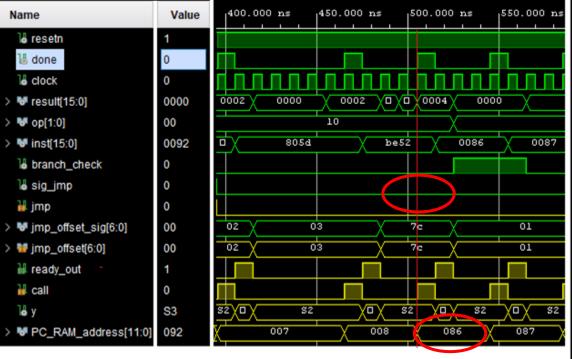

#### Aside: An extremely small timing error

Block Overview Data Path

Program Counter 7- Seg Serializer Program

#### "branch\_check" flips once after 520 ns

- Flip last for infinitely short period of time

- Resolved by adding clock event check

```

when S2 =>

-- Added clock check to stop simulation error

if (clock'event and clock = '1') then

if call = '1' then

if jmp = '1' then

-- Jump Ram Address

if jmp_dir = '1' then

-- Negative

PC_RAM_address <= PC_RAM_address - conv std logic vector (unsigned(jmp_offset_invert plus),NA-1);

else

-- Positive

PC_RAM_address <= PC_RAM_address + conv std logic vector (unsigned(jmp_offset),NA-1);

end if;

else

-- No Jump, index by 1

PC_RAM_address <= PC_RAM_address + conv_std_logic_vector (1,NA-1);</pre>

end if;

end if;

end if;

```

Block Overview Data Path

Program Counter 7- Seg Serializer Program

- Original program counter failed in post-synthesis timing

- Unmapped synthesized ram signals

- Possibly result of using two in\_RAMgen

Data Path

- Revised PC uses LUT

- Loads from text file

Block

Overview

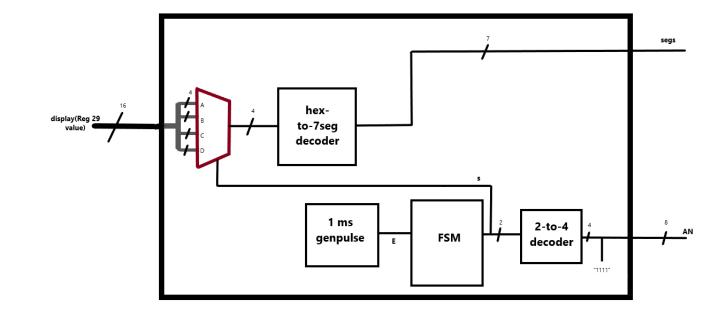

### Serializer

Takes constant output from register 29, the "output" register

## Basic parametric code, important to the real life applications of our microprocessor

Block Overview Data Path

Program Counter 7- Seg Serializer Program

### Machine Code Instructions

Table shows the different machine code inputs for the functions in our microprocessor

| Bit:         | 15 | 14   | 1                                | 3 12     | 11      | 10      | 9         | 8 | 7             | 6        | 5 | 4 3       | 2             | 1       | 0 | Instruction    |

|--------------|----|------|----------------------------------|----------|---------|---------|-----------|---|---------------|----------|---|-----------|---------------|---------|---|----------------|

| Logic:       | 0  | 0    | Des                              | tination | Registe | er/Regi | ster A    |   | Reg           | jister B | 1 | Fi        | unction (     | Dp Code |   |                |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 0             | 0       | - | A = Not A      |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 0             | 0       | 1 | B = Not B      |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 0             | 1       | 0 | A = A and B    |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 0             | 1       | 1 | A = A or B     |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 1             | 0       | 0 | A = A nand B   |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 1             | 0       | 1 | A = A nor B    |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 1             | 1       | 0 | A = A xor B    |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   | x         | 1             | 1       | 1 | A = A xnor B   |

|              | 0  | 0    |                                  |          |         |         |           |   |               |          |   |           |               |         |   |                |

| Arithmatic:  | 0  | 1    | Destination Register/ Register A |          |         |         |           |   | Register B Fi |          |   | unction ( | Dp Code       | 8       |   |                |

|              | 0  | 1    | 96<br>1                          |          |         |         |           |   |               |          |   | 0         | 0             | 0       | 0 | A = A + 1      |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   | 0         | 0             | 0       | 1 | B = B + 1      |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   | 0         | 0             | 1       | 0 | A = A - 1      |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   | 0         | 0             | 1       | 1 | B = B - 1      |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   | 0         | 1             | 0       | 0 | A = A + B      |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   | 0         | 1             | 0       | 1 | A = A - B      |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   | 0         | 1             | 1       | 1 | B = A          |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   |           |               |         |   |                |

|              | 0  | 1    |                                  |          |         |         |           |   |               |          |   |           |               |         |   |                |

| Move/Stack:  | 1  | 0    | Offset High Bits                 |          |         |         |           |   | Offs          |          |   | Offse     | Offset Low OP |         |   |                |

|              | 1  | 0    | dir                              | off(5)   | off(4)  | off(3)  | off(2)    |   |               |          |   | off(1)    | off(0)        | 0       | 0 | JMP            |

|              | 1  | 0    | dir                              | off(5)   | off(4)  |         | 100000000 |   |               |          |   | off(1)    | off(0)        | 1       | 0 | BRN if B = 0   |

|              | 1  | 0    | dir                              | off(5)   | off(4)  | off(3)  | 23971     |   |               |          |   | 1.15.79   | off(0)        | 1       | 1 | BRN if B is -  |

|              | 1  | 0    | x                                | x        | x       | x       | x         |   |               |          |   | 0         |               | 0       | 1 | SP = SP + 1    |

|              | 1  |      | х                                | x        | x       | x       | x         |   |               |          |   | 0         | 164           | 0       |   | SP = SP - 1    |

|              | 1  |      | x                                | x        | x       | x       | x         |   |               |          |   | 1         | 0             | 0       | 1 | Push to stack  |

|              | 1  | 1111 | х                                | x        | x       | x       | x         |   |               |          |   | 1         | 7.4           | 0       |   | Pull from stat |

|              | 1  | 0    | 4329                             |          |         |         |           |   |               |          |   |           | 191           |         |   |                |

| Load IM(R30) | 1  | 1    | 83                               |          |         |         | <u> </u>  | 1 | oad V         | alue     |   | 1.2       |               |         | - |                |

### Test Program

| Name                     | Value    | 4,200.000 ns 14,300.000 ns 14,400.000 ns 14,500.000 ns 14,600.000 ns 14,700.000 ns 14,800.000 ns 14,900.000         |

|--------------------------|----------|---------------------------------------------------------------------------------------------------------------------|

| 16 resetn                | 1        |                                                                                                                     |

| La clock                 | 0        |                                                                                                                     |

| 🔓 done                   | 0        |                                                                                                                     |

| stop_error_out           | 0        |                                                                                                                     |

| > 😻 segs[6:0]            | 4f       | 4f                                                                                                                  |

| > 😽 AN[7:0]              | fe       | fe                                                                                                                  |

| U T                      | 10000 ps | 10000 ps                                                                                                            |

| > V PC_RAM_address[11:0] | 007      | <u>008% 006 007 % 009 % 00a % 006 % 004 % 006 % 007 % 008 % 006 % 007 % 008 % 006 % 007 % 008 % 006 % 007 % 008</u> |

| > 🖬 R2                   | 0002     |                                                                                                                     |

| > 🖬 R3                   | 0002     | 0001                                                                                                                |

| > 🖬 R29                  | 0001     |                                                                                                                     |

|                          |          |                                                                                                                     |

| Name                     | Value    | 4,700.000 ns 4,800.000 ns 4,900.000 ns 5,000.000 ns 5,100.000 ns 5,200.000 ns 5,300.000 ns 5,400.000 ns             |

| le resetn                | 1        |                                                                                                                     |

| clock                    | 0        |                                                                                                                     |

| 🖥 done                   | 0        |                                                                                                                     |

| stop_error_out           | 0        | سنس تسنست متستى تصديحا سنست سنست متستى تستحي استعر                                                                  |

| > 😽 segs[6:0]            | 4f       | 4f 12                                                                                                               |

| > 😼 AN[7:0]              | fe       | fe                                                                                                                  |

| ₩ т                      | 10000 ps | 10000 ps                                                                                                            |

| V PC_RAM_address[11:0]   | 007      | 007 008 006 007 008 006 007 008 006 007 008 006 007 009 00a 000 001 002 003 004 005 006 007                         |

| > 👹 R2                   | 0002     |                                                                                                                     |

| > 🖬 R3                   | 0002     | 0001 0006                                                                                                           |

| > 🖬 R29                  | 0001     | 0001 0002                                                                                                           |

|                          |          |                                                                                                                     |

|                          | Block    | Data Path Program 7- Seg                                                                                            |

|                          | DIUCK    |                                                                                                                     |

| 4200;<br>000                                               | R1 = R1 + 1                            | PC:       |  |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------|-----------|--|--|--|--|--|--|--|

| 43E7;                                                      | R29(output) = R1                       | PC: 001   |  |  |  |  |  |  |  |

| C006;                                                      | IM = 6                                 | PC: 002   |  |  |  |  |  |  |  |

| 7E37;                                                      | R3 = IM                                | PC:       |  |  |  |  |  |  |  |

| 003                                                        |                                        |           |  |  |  |  |  |  |  |

| C005;                                                      | IM = 5                                 | PC:       |  |  |  |  |  |  |  |

| 004                                                        |                                        |           |  |  |  |  |  |  |  |

| 7E27;                                                      | R2 = IM                                | PC:       |  |  |  |  |  |  |  |

| 005                                                        |                                        |           |  |  |  |  |  |  |  |

| 4402;                                                      | R2 = R2 - 1                            | PC:       |  |  |  |  |  |  |  |

| 006                                                        |                                        |           |  |  |  |  |  |  |  |

| 802A;                                                      | Branch to 009 if $R2 = 0$              | PC: 007   |  |  |  |  |  |  |  |

| BE38;                                                      | JMP to 006                             | PC:       |  |  |  |  |  |  |  |

| 008                                                        |                                        |           |  |  |  |  |  |  |  |

| 4602;                                                      | R3 = R3 - 1                            | PC:       |  |  |  |  |  |  |  |

|                                                            | ler to demonstrate this counte         | <u> </u>  |  |  |  |  |  |  |  |

|                                                            | l, Breavellesiopoot to Reg-2 on        |           |  |  |  |  |  |  |  |

|                                                            | ელ <b>Mp ∉ე∈ეიდ</b> -µa 1 second delay |           |  |  |  |  |  |  |  |

| 00B instruction takes about 40 ns, FFFF is loaded into R2  |                                        |           |  |  |  |  |  |  |  |

| and 007F is loaded into R3 to create approximately a 1     |                                        |           |  |  |  |  |  |  |  |

| second delay, incrementing the value of the output         |                                        |           |  |  |  |  |  |  |  |

| register every 1 second. This calculation takes the timing |                                        |           |  |  |  |  |  |  |  |

| for the                                                    | e jump instructions into consid        | leration. |  |  |  |  |  |  |  |

|                                                            |                                        |           |  |  |  |  |  |  |  |

BIOCK Overview Program

7- Seg Serializer Program

Block Overview