# **CAN Controller**

John Brooks Evan Manser Emad Eissa April 23, 2020

#### SERIAL DATA PROCESSOR

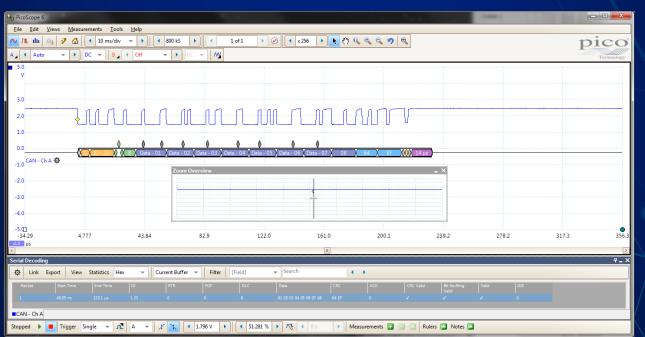

- Samples bits on the CAN bus.

- Synchronizes on rising / falling edges.

#### **DESTUFFER**

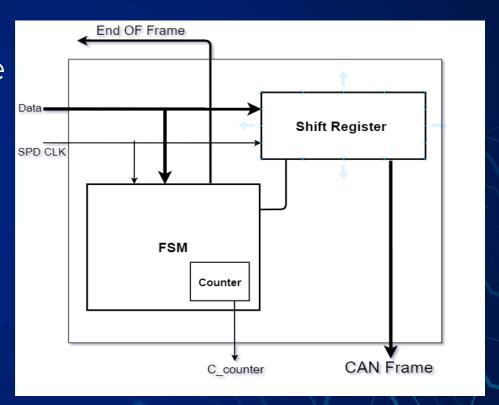

Using Shift register, counter, and the FSM, the destuffer's main task is to filter the main data layout the actual CAN Frame Also, the destuffer provides the bit count signal for the rest of the system.

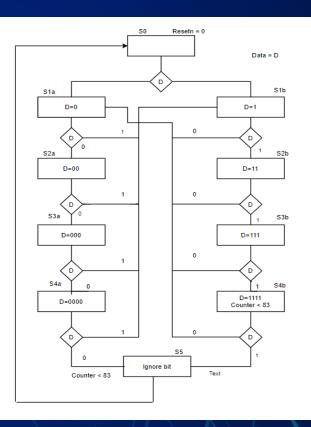

### **DESTUFFER FSM**

FSM designed by containing ten states. Simple and efficient design.

Finally, The Destuffer sends EOF signal at the End of CAN Frame and wait for some time then Clear the counter and register.

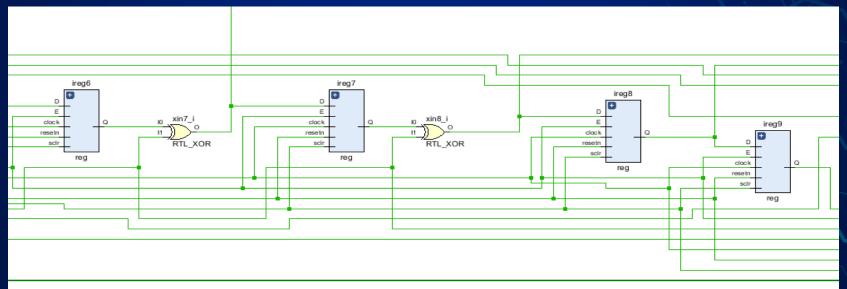

### CYCLIC REDUNDANCY CHECK (CRC)

- Polynomial = X<sup>15</sup> + X<sup>14</sup> + X<sup>10</sup> + X<sup>8</sup> + X<sup>7</sup> + X<sup>4</sup> + X<sup>3</sup> +

- Registers and XOR gates

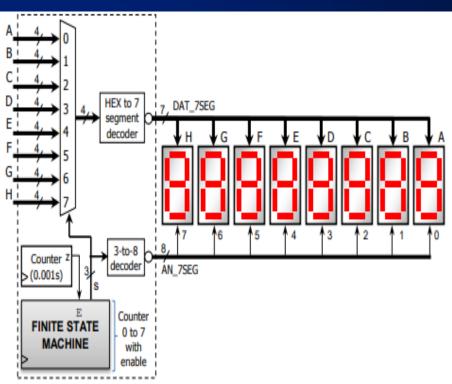

### DATA EXTRACTION AND OUTPUT

ARB\_ID and ACK

enabled Res

Seven-Segment

Seria

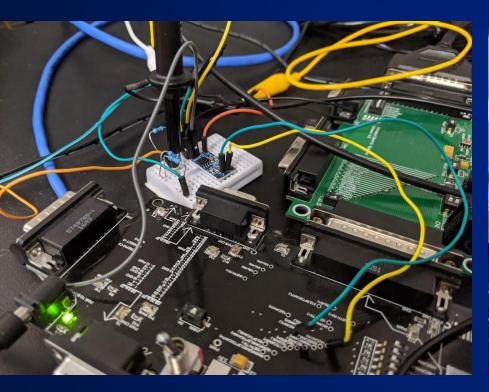

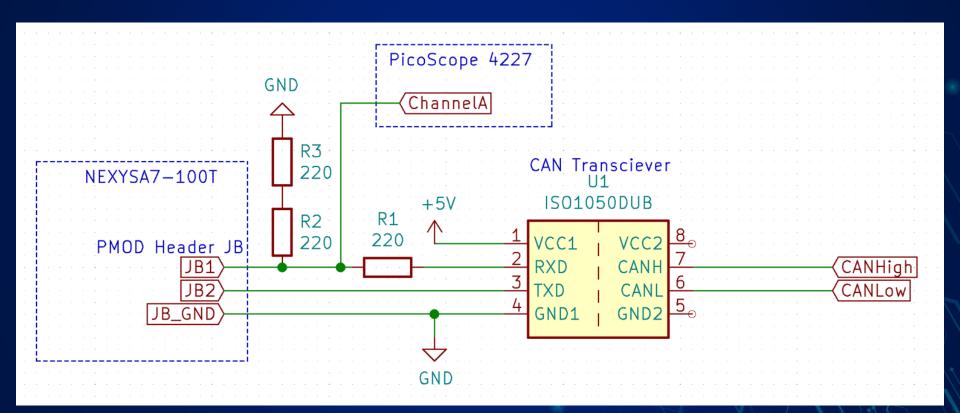

# **Electrical Assembly**

## **Electrical Assembly**

### **CONCLUSION AND SUMMARY**

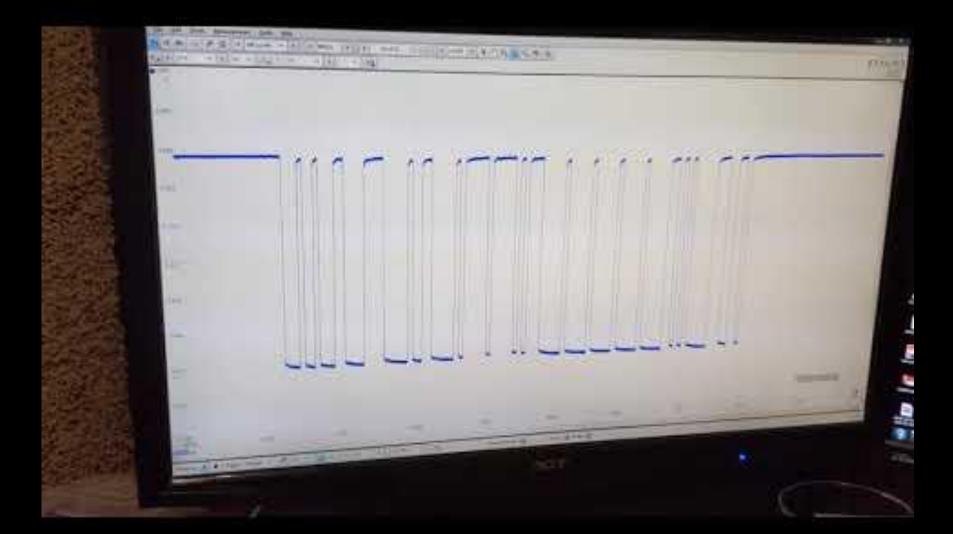

- Fully functional in behavioural simulation

- 2. Physical implementation mostly functional

- 3. Generates CAN data output to seven segment display