# Bosch Controller Area Network (CAN) Version 2.0

PROTOCOL STANDARD

| 2  | BASIC CONCEPTS                              |        |

|----|---------------------------------------------|--------|

| 3  | MESSAGE TRANSFER                            |        |

| 4  | ERROR HANDLING                              |        |

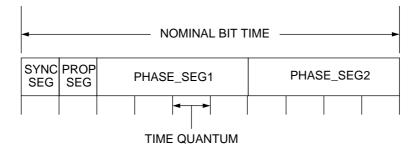

| 5  | FAULT CONFINEMENT                           | j      |

| 6  | BIT TIMING REQUIREMENTS                     | , I    |

| 7  | INCREASING OSCILLATOR TOLERANCE             | 101    |

| 8  | INTRODUCTION                                | סחם    |

| 9  | BASIC CONCEPTS                              | COD    |

| 10 | MESSAGE TRANSFER                            |        |

| 11 | ERROR HANDLING                              | S<br>C |

| 12 | FAULT CONFINEMENT                           |        |

| 13 | BIT TIMING REQUIREMENTS                     | 000    |

| A  | THE MOTOROLA CAN (MCAN) MODULE              | T      |

| В  | TOUCAN                                      |        |

| C  | THE MOTOROLA SCALEABLE CAN (MSCAN08) MODULE |        |

| D  | THE MOTOROLA SCALEABLE CAN (MSCAN12) MODULE |        |

|    |                                             |        |

INTRODUCTION

|    | Freescale Semiconductor, Inc.               |

|----|---------------------------------------------|

| 1  | INTRODUCTION                                |

| 2  | BASIC CONCEPTS                              |

| 3  | MESSAGE TRANSFER                            |

| 4  | ERROR HANDLING                              |

| 5  | FAULT CONFINEMENT                           |

| 6  | BIT TIMING REQUIREMENTS                     |

| 7  | INCREASING OSCILLATOR TOLERANCE             |

| 8  | INTRODUCTION                                |

| 9  | BASIC CONCEPTS                              |

| 10 | MESSAGE TRANSFER                            |

| 11 | ERROR HANDLING                              |

| 12 | FAULT CONFINEMENT                           |

| 13 | BIT TIMING REQUIREMENTS                     |

| A  | THE MOTOROLA CAN (MCAN) MODULE              |

| В  | TOUCAN                                      |

| C  | THE MOTOROLA SCALEABLE CAN (MSCAN08) MODULE |

| D  | THE MOTOROLA SCALEABLE CAN (MSCAN12) MODULE |

# Bosch Controller Area Network Version 2.0 Protocol Standard

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 'Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

© MOTOROLA LTD., 1998

# **Conventions**

Where abbreviations are used in the text, an explanation can be found in the glossary, at the back of this manual. Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Unless otherwise stated, shaded cells in a register diagram indicate that the bit is either unused or reserved; 'u' is used to indicate an undefined state (on reset).

- Cut along this line to remove

# Freescale Semiconductor, Inc.

### **CUSTOMER FEEDBACK QUESTIONNAIRE (CAN PROTOCOL)**

Motorola wishes to continue to improve the quality of its documentation. We would welcome your feedback on the publication you have just received. Having used the document, please complete this card (or a photocopy of it, if you prefer).

| 1. | How would you                                                                           | rate the q     | uality of t       | he docı  | ument? Chec     | k one box in each catego                                            | ory.         |         |           |         |              |

|----|-----------------------------------------------------------------------------------------|----------------|-------------------|----------|-----------------|---------------------------------------------------------------------|--------------|---------|-----------|---------|--------------|

|    |                                                                                         | Exc            | ellent            |          | Poor            |                                                                     | Excelle      | nt      |           | Poor    |              |

|    | Organization<br>Readability<br>Understandabil<br>Accuracy<br>Illustrations<br>Comments: | ity [          |                   |          | 0000            | Tables Table of contents Index Page size/binding Overall impression | 00000        | 00000   |           |         |              |

| 2. | What is your int                                                                        | ended us       | e for this        | docume   | ent? If more to | nan one option applies, p                                           | olease rank  | them (  | 1, 2, 3). |         |              |

|    | Selection of dev                                                                        | vice for ne    | w applica         | tion     |                 | Other  Pleas                                                        | e specify:   |         |           |         |              |

|    | System design                                                                           |                |                   |          | ∺               | _                                                                   |              |         |           |         |              |

|    | Training purpos                                                                         | es             |                   |          | ∺               |                                                                     |              |         |           |         |              |

|    |                                                                                         |                |                   |          | _               |                                                                     |              |         |           |         |              |

| 3. | How well does                                                                           | this manu      | al enable         | you to p | perform the t   | ask(s) outlined in questio                                          | n 2?         |         |           |         |              |

|    |                                                                                         | Com            | pletely           |          | Not at all      | Comments:                                                           |              |         |           |         |              |

|    |                                                                                         |                |                   |          |                 |                                                                     |              |         |           |         |              |

| 4. | How easy is it to                                                                       | o find the     | — —<br>informatio | on you a | are looking fo  | r?                                                                  |              |         |           |         |              |

|    | ,                                                                                       |                | asy               | •        | Difficult       | Comments:                                                           |              |         |           |         |              |

|    |                                                                                         | Г              | ,<br>1            |          |                 |                                                                     |              |         |           |         |              |

|    |                                                                                         | -              |                   | _        | _               |                                                                     |              |         |           |         |              |

| 5. | Is the level of te                                                                      | echnical de    | etail in the      | followi  | ng sections s   | sufficient to allow you to u                                        | understand   | how the | e devic   | e funct | ions?        |

|    |                                                                                         |                |                   |          |                 |                                                                     | Too little o | detail  |           | Too     | o much detai |

|    | SECTION 1                                                                               | INTROD         | UCTION            |          |                 |                                                                     |              |         |           |         |              |

|    | SECTION 2                                                                               | BASIC C        | CONCEPT           | rs       |                 |                                                                     |              |         |           |         |              |

|    | SECTION 3                                                                               | MESSAG         | GE TRAN           | SFER     |                 |                                                                     |              |         |           |         |              |

|    | SECTION 4                                                                               | ERROR          | HANDLI            | ١G       |                 |                                                                     |              |         |           |         |              |

|    | SECTION 5                                                                               | FAULT C        | ONFINE            | MENT     |                 |                                                                     |              |         |           |         |              |

|    | SECTION 6                                                                               | BIT TIMI       | NG REQ            | JIREMI   | ENTS            |                                                                     |              |         |           |         |              |

|    | SECTION 7                                                                               | INCREA         | SING OS           | CILLAT   | OR TOLERA       | NCE                                                                 |              |         |           |         |              |

|    | SECTION 8                                                                               |                | YSICAL L          | .AYER    |                 |                                                                     |              |         |           |         |              |

|    | SECTION 9                                                                               | INTROD         |                   |          |                 |                                                                     |              |         |           |         |              |

|    | SECTION 10                                                                              |                | CONCEPT           |          |                 |                                                                     |              |         |           |         |              |

|    | SECTION 11                                                                              |                | GE TRAN           |          |                 |                                                                     |              |         |           |         |              |

|    | SECTION 12                                                                              |                |                   |          |                 |                                                                     |              |         |           |         |              |

|    | SECTION 13                                                                              |                |                   |          |                 |                                                                     |              |         |           |         |              |

|    | SECTION A                                                                               |                |                   | CAN (I   | MCAN) MOD       | ULE                                                                 |              |         |           |         |              |

|    | SECTION B                                                                               | TOUCAN         |                   |          |                 |                                                                     | <u> </u>     | Ш       |           |         | ╚            |

|    | SECTION C                                                                               |                |                   |          |                 | (MSCAN08) MODULE                                                    | <u> </u>     |         |           |         |              |

|    | SECTION D                                                                               |                |                   |          |                 | (MSCAN12) MODULE                                                    |              | Ш       |           |         |              |

| ó. | Have you found                                                                          | any errors     | s? If so, p       | lease c  | omment:         |                                                                     |              |         |           |         |              |

| ,  |                                                                                         | - <b>f</b> . d |                   |          |                 |                                                                     |              |         |           |         |              |

| 7. | From your point                                                                         | of view, is    | anytning          | missin   | y from the do   | ocument? If so, please sa                                           | ıy wnat:     |         |           |         |              |

|   | 1  |

|---|----|

| 1 | 4  |

| ١ | 1  |

| • | •  |

| _ | ١. |

| σ | ,  |

|   |    |

Cut along this line to remove

First fold back along this line

| 0          |

|------------|

|            |

|            |

| 7          |

| 0          |

| 7          |

|            |

|            |

| •          |

|            |

| 9          |

|            |

|            |

| ם          |

|            |

|            |

| <b>(1)</b> |

|            |

|            |

| 70         |

| Û          |

| <b>D</b>   |

| _          |

| ь.         |

|            |

|            |

|            |

| 9.  | How would you rate Motorola's documentation?                                |

|-----|-----------------------------------------------------------------------------|

|     | Excellent Poor                                                              |

|     | - In general                                                                |

|     | - Against other semiconductor suppliers                                     |

| 10. | Which semiconductor manufacturer provides the best technical documentation? |

| 11. | Which company (in any field) provides the best technical documentation?     |

| 12. | How many years have you worked with microprocessors?                        |

|     | Less than 1 year 1–3 years 3–5 years More than 5 years                      |

|     | - Second fold back along this line -                                        |

|     |                                                                             |

|     |                                                                             |

# REPONSE PAYEE GRANDE-BRETAGNE

NO STAMP REQUIRED

Motorola Ltd., Colvilles Road, Kelvin Industrial Estate, EAST KILBRIDE, G75 8BR. GREAT BRITAIN.

F.A.O. Technical Publications Manager (re: BCANPSV2.0/D)

IBRS NUMBER PHQ-B/207/G CCRI NUMERO PHQ-B/207/G

| - Third fold back along this line - | _ |

|-------------------------------------|---|

|                                     |   |

| 3. | ,               | s some discussion in the semiconductor industry regarding a move towards providing data sheets in electron<br>e any opinion on this subject, please comment. | nic |

|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4. | We would be g   | ateful if you would supply the following information (at your discretion), or attach your card.                                                              |     |

|    | Name:           | Phone No:                                                                                                                                                    |     |

|    | Position:       | FAX No:                                                                                                                                                      |     |

|    | Department:     |                                                                                                                                                              |     |

|    | Company:        |                                                                                                                                                              |     |

|    | Address:        |                                                                                                                                                              |     |

|    |                 |                                                                                                                                                              |     |

|    | Thank you for I | elping us improve our documentation                                                                                                                          |     |

Thank you for helping us improve our documentation, Technical Publications Manager, Motorola Ltd., Scotland.

For More Information On This Product, Go:/to:/www.dreespale.com

# **TABLE OF CONTENTS**

| Paragraph |       | Page   |

|-----------|-------|--------|

| Number    | TITLE | Number |

### **PART A**

# 1 INTRODUCTION

# 2 BASIC CONCEPTS

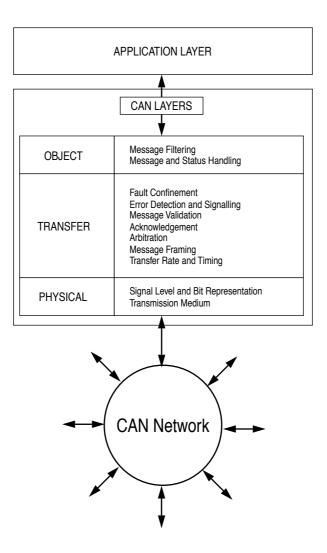

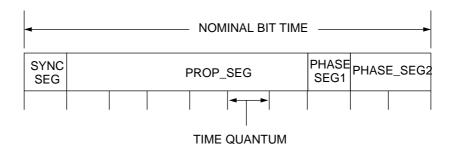

| 2.1     | Layered structure of a CAN node    | 2-1   |

|---------|------------------------------------|-------|

| 2.2     | Messages                           |       |

|         | · · · · ·                          |       |

| 2.2.1   | Information routing                |       |

| 2.2.1.1 | 1 System flexibility               | . 2-1 |

| 2.2.1.2 | 2 Message routing                  | 2-2   |

| 2.2.1.3 | 3 Multicast                        | 2-3   |

| 2.2.1.4 | 4 Data consistency                 | 2-3   |

| 2.3     | Bit-rate                           | 2-3   |

| 2.4     | Priorities                         | 2-3   |

| 2.5     | Remote data request                | 2-3   |

| 2.6     | Multi-master                       | . 2-3 |

| 2.7     | Arbitration                        | 2-4   |

| 2.8     | Data integrity                     | . 2-4 |

| 2.8.1   | Error detection                    | . 2-4 |

| 2.8.2   | Performance of error detection     | 2-5   |

| 2.9     | Error signalling and recovery time | 2-5   |

| 2.10    | Fault confinement                  | . 2-5 |

| 2.11    | Connections                        | 2-5   |

| 2.12    | Single channel                     | 2-6   |

| 2.13    | Bus values                         | 2-6   |

| 2.14    | Acknowledgement                    | 2-6   |

| 2.15    | Sleep mode/wake-up                 | 2-6   |

| Paragraph |  |

|-----------|--|

| Number    |  |

### **TABLE OF CONTENTS**

Page Number

# **MESSAGE TRANSFER**

| 3.1     | Definition of transmitter/receiver | 2.4      |

|---------|------------------------------------|----------|

|         | Definition of transmitter/receiver |          |

| 3.1.1   | Transmitter                        | -        |

| 3.1.2   | Receiver                           |          |

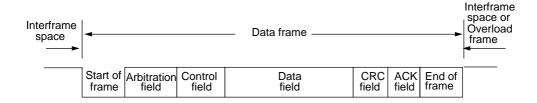

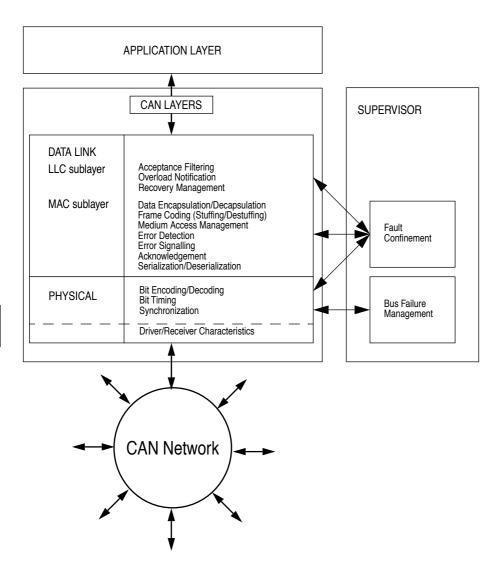

| 3.2     | Frame types                        | 3-1      |

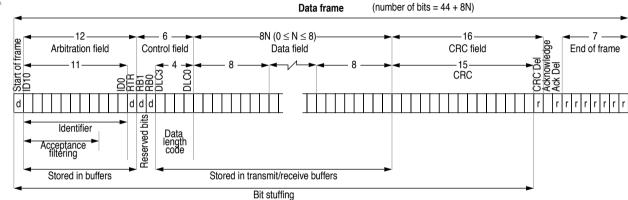

| 3.2.1   | Data frame                         |          |

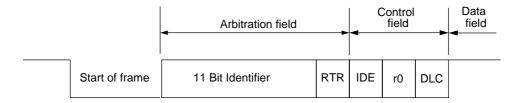

| 3.2.1.1 | Start of frame                     | 3-2      |

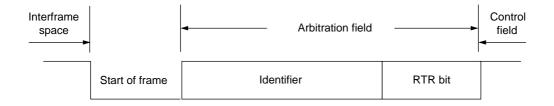

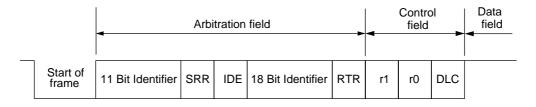

| 3.2.1.2 | Arbitration field                  | 3-2      |

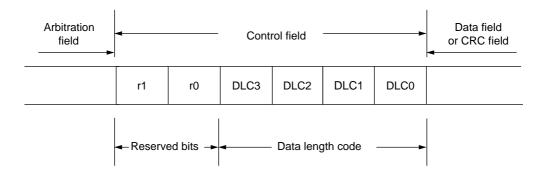

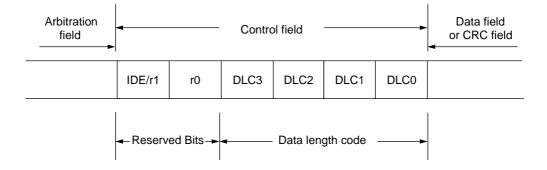

| 3.2.1.3 | Control field                      | 3-3      |

| 3.2.1.4 | Data field                         | 3-3      |

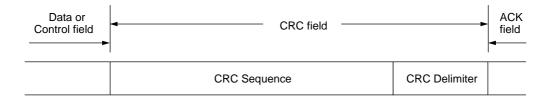

| 3.2.1.5 | CRC field                          | 3-4      |

| 3.2.1.6 | ACK field                          | 3-5      |

| 3.2.1.7 | End of frame                       | 3-6      |

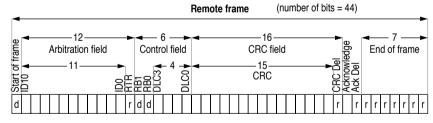

| 3.2.2   | Remote frame                       | 3-6      |

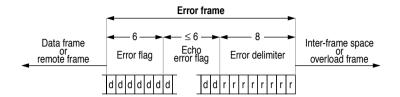

| 3.2.3   | Error frame                        | 3-7      |

| 3.2.3.1 | Error flag                         | 3-7      |

| 3.2.3.2 | Pror Delimiter                     | 3-8      |

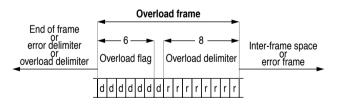

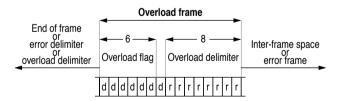

| 3.2.4   | Overload frame                     | 3-8      |

| 3.2.4.1 | Overload flag                      | 3-9      |

| 3.2.4.2 | 2 Overload Delimiter               | 3-9      |

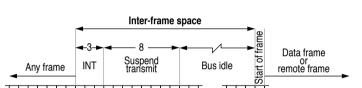

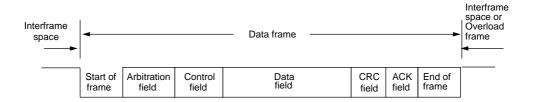

| 3.2.5   | Interframe space                   | 3-9      |

| 3.2.5.1 |                                    |          |

| 3.2.5.2 | Bus idle                           | 3-10     |

| 3.2.5.3 | Suspend transmission               | 3-13     |

| 3.3     | Message validation                 |          |

| 3.3.1   | Transmitter                        |          |

| 3.3.2   | Receiver                           | -        |

| 3.4     | Bit-stream coding                  |          |

|         | g                                  | <b>U</b> |

|         |                                    |          |

# **ERROR HANDLING**

| 4.1   | Error detection       | 4-1 |

|-------|-----------------------|-----|

| 4.1.1 | Bit error             | 4-1 |

| 4.1.2 | Stuff error           | 4-1 |

| 4.1.3 | CRC error             | 4-1 |

| 4.1.4 | Form error            | 4-2 |

|       | Acknowledgement error |     |

|       | Error signalling      |     |

|       |                       |     |

| Paragrap<br>Number | TABLE OF CONTENTS                                                   | Page<br>Number |

|--------------------|---------------------------------------------------------------------|----------------|

|                    | 5 FAULT CONFINEMENT                                                 |                |

| 5.1<br>5.2         | CAN node status                                                     |                |

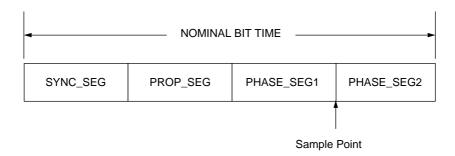

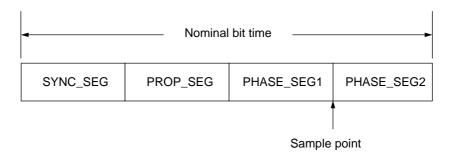

|                    | 6 BIT TIMING REQUIREMENTS                                           |                |

| 6.1                | Nominal bit rate                                                    | 6-1            |

| 6.2                | Nominal bit time                                                    | 6-1            |

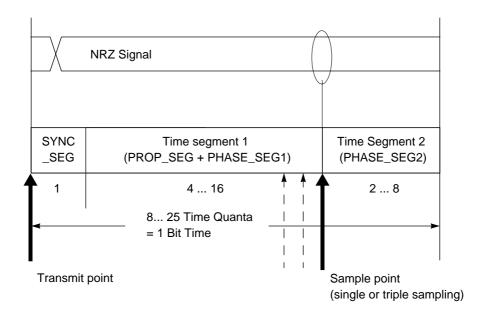

| 6.3                | SYNC_SEG                                                            | 6-2            |

| 6.4                | PROP_SEG                                                            |                |

| 6.5                | PHASE_SEG1, PHASE_SEG2                                              | 6-2            |

| 6.6                | Sample point                                                        |                |

| 6.7                | Information processing time                                         |                |

| 6.8                | Time quantum                                                        |                |

| 6.8.1              | Length of time segments                                             |                |

| 6.9                | Synchronization                                                     |                |

| 6.9.1              | Hard synchronization                                                |                |

| 6.9.2              | Resynchronization jump width                                        |                |

| 6.9.3              | Phase error of an edge                                              |                |

| 6.9.4              | Resynchronization                                                   |                |

| 6.9.5              | Synchronization rules                                               | 6-4            |

|                    | 7 INCREASING OSCILLATOR TOLERANCE                                   |                |

| 7.1                | Protocol modifications                                              | 7.4            |

| 7.1                | Determination of the maximum synchronization length                 |                |

| 7.2<br>7.2.1       | Local error, where at least two of the nodes are Error ACTIVE       |                |

| 7.2.1              | Two consecutive Overload frames                                     |                |

| 7.2.2              | Acknowledge error at transmitter, where all nodes are Error PASSIVE |                |

| 7.2.3              | Local error at transmitter, where all nodes are Error PASSIVE       |                |

| 7.2.4              | Bit timing                                                          |                |

| 7.3.1              | Construction of the bit timing for maximum oscillator tolerance     |                |

| 7.3.1              | Construction of the bit timing for maximum bit rate                 |                |

| 7.3.2              | Calculation of the oscillator tolerance                             |                |

| 7.5                | Maximum oscillator tolerances                                       |                |

| 7.5<br>7.5.1       | Oscillator tolerance for existing CAN protocol                      |                |

| 7.5.1              | Oscillator tolerance for enhanced CAN protocol                      |                |

| 7.5.2              | Resynchronization                                                   |                |

| 7.7                | Compatibility of existing and enhanced CAN protocols                |                |

| 7.8                | Assessment                                                          |                |

|                    | , 00000                                                             |                |

Paragraph Number

### **TABLE OF CONTENTS**

Page Number

### **PART B**

### 8 **INTRODUCTION**

# **BASIC CONCEPTS**

| 9.1     | Layered structure of a CAN node    | 9-1 |

|---------|------------------------------------|-----|

| 9.2     | Messages                           |     |

| 9.2.1   | Information routing                |     |

| 9.2.1.1 | System flexibility                 | 9-2 |

| 9.2.1.2 | 2 Message routing                  | 9-3 |

| 9.2.1.3 | B Multicast                        | 9-3 |

| 9.2.1.4 | Data consistency                   | 9-3 |

| 9.3     | Bit-rate                           | 9-3 |

| 9.4     | Priorities                         | 9-3 |

| 9.5     | Remote data request                | 9-3 |

| 9.6     | Multi-master                       | 9-4 |

| 9.7     | Arbitration                        | 9-4 |

| 9.8     | Data integrity                     | 9-4 |

| 9.8.1   | Error detection                    | 9-4 |

| 9.8.2   | Performance of error detection     | 9-5 |

| 9.9     | Error signalling and recovery time | 9-5 |

| 9.10    | Fault confinement                  | 9-5 |

| 9.11    | Connections                        | 9-5 |

| 9.12    | Single channel                     | 9-6 |

| 9.13    | Bus values                         | 9-6 |

| 9.14    | Acknowledgement                    | 9-6 |

| 9.15    | Sleep mode/wake-up                 | 9-6 |

| 9.16    | Oscillator Tolerance               | 9-7 |

|         |                                    |     |

|         |                                    |     |

|         | 10                                 |     |

# **MESSAGE TRANSFER**

| 10.1   | Definition of transmitter/receiver | 10-1 |

|--------|------------------------------------|------|

| 10.1.1 | Transmitter                        | 10-1 |

| 10.1.2 | Receiver                           | 10-1 |

| 10.2   | Frame formats                      | 10-1 |

| 10.3   | Frame types                        | 10-1 |

| 10.3.1 | Data frame                         | 10-2 |

| 10.3.1 | .1 Start of frame                  | 10-2 |

| Paragraph<br>Number | TABLE OF CONTENTS                               | Page<br>Numbe |

|---------------------|-------------------------------------------------|---------------|

| 10.3.1.2            | Arbitration field                               | 10-3          |

| 10.3.1.3            | Control field                                   | 10-4          |

| 10.3.1.4            | Data field                                      | 10-5          |

| 10.3.1.5            | CRC field (Standard Format and Extended Format) | 10-6          |

| 10.3.1.6            | ACK field (Standard Format and Extended Format) |               |

| 10.3.1.7            | End of frame                                    |               |

| 10.3.2              | Remote frame                                    | 10-8          |

| 10.3.3              | Error frame                                     | 10-8          |

| 10.3.3.1            | Error flag                                      | 10-9          |

| 10.3.3.2            | Error delimiter                                 | 10-9          |

| 10.3.4              | Overload frame                                  | 10-10         |

| 10.3.4.1            | Overload flag                                   | 10-11         |

| 10.3.4.2            | Overload delimiter                              | 10-11         |

| 10.3.5              | Interframe space                                | 10-11         |

| 10.3.5.1            | INTERMISSION                                    | 10-12         |

| 10.3.5.2            | Bus idle                                        | 10-13         |

| 10.3.5.3            | Suspend transmission                            | 10-13         |

| 10.4 C              | onformance with regard to frame formats         | 10-13         |

| 10.5 M              | essage filtering                                | 10-13         |

| 10.6 M              | essage validation                               | 10-17         |

| 10.6.1              | Transmitter                                     | 10-17         |

| 10.6.2              | Receiver                                        | 10-17         |

| 10.7 Bi             | t-stream coding                                 | 10-17         |

|                     | 11<br>ERROR HANDLING                            |               |

| 11.1 Ei             | ror detection                                   |               |

| 11.1.1              | Bit error                                       | 11-1          |

| 11.1.2              | Stuff error                                     | 11-1          |

| 11.1.3              | CRC error                                       |               |

| 11.1.4              | Form error                                      |               |

| 11.1.5              | Acknowledgement error                           | 11-2          |

| 11.2 Eı             | ror signalling                                  | 11-2          |

|                     | 12 FAULT CONFINEMENT                            |               |

| 40.4                |                                                 |               |

|                     | AN node status                                  |               |

| 12.2 Fi             | ror counts                                      | 12-1          |

| Paragraph<br>Number | TABLE OF CONTENTS | Page<br>Number |

|---------------------|-------------------|----------------|

|                     |                   |                |

| 13 BIT TIMING REQUIREMENTS |                                                      |     |  |

|----------------------------|------------------------------------------------------|-----|--|

|                            |                                                      |     |  |

| 13.1                       | Nominal bit rate1                                    |     |  |

| 13.2                       | Nominal bit time                                     |     |  |

| 13.3                       | SYNC_SEG1                                            |     |  |

| 13.4                       | PROP_SEG1                                            |     |  |

| 13.5                       | PHASE_SEG1, PHASE_SEG21                              |     |  |

| 13.6                       | Sample point                                         | 3-2 |  |

| 13.7                       | Information processing time                          |     |  |

| 13.8                       | Time quantum                                         |     |  |

| 13.8.1                     | Length of time segments                              |     |  |

| 13.9                       | Synchronization                                      |     |  |

| 13.9.1                     | Hard synchronization1                                |     |  |

| 13.9.2                     | Resynchronization jump width1                        |     |  |

| 13.9.3                     | Phase error of an edge1                              |     |  |

| 13.9.4                     | Resynchronization                                    |     |  |

| 13.9.5                     | Synchronization rules                                | 3-5 |  |

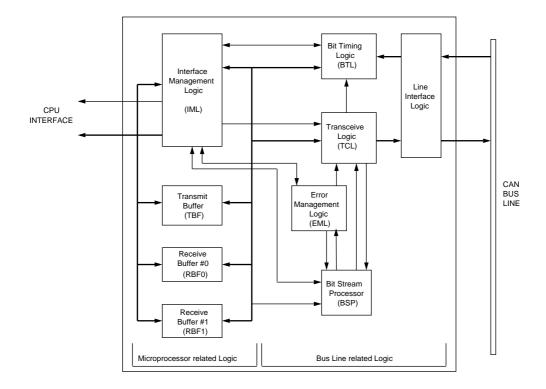

|                            | THE MOTOROLA CAN (MCAN) MODULE                       |     |  |

| A.1                        | Functional overview                                  |     |  |

| A.1.1                      | IML – interface management logic                     |     |  |

| A.1.2                      | TBF – transmit buffer                                |     |  |

| A.1.3                      | RBF – receive buffer                                 |     |  |

| A.1.4<br>A.1.5             | BSP – bit stream processor                           |     |  |

|                            | BTL – bit timing logic                               |     |  |

| A.1.6<br>A.1.7             | TCL – transceive logic  EML – error management logic |     |  |

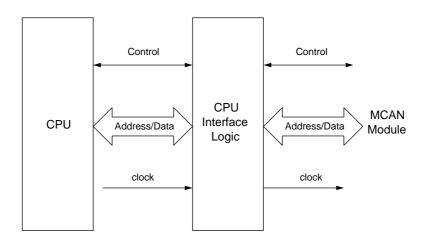

| A.1.7<br>A.2               | MCAN interface                                       |     |  |

| A.2.1                      | CIL – controller interface unit                      |     |  |

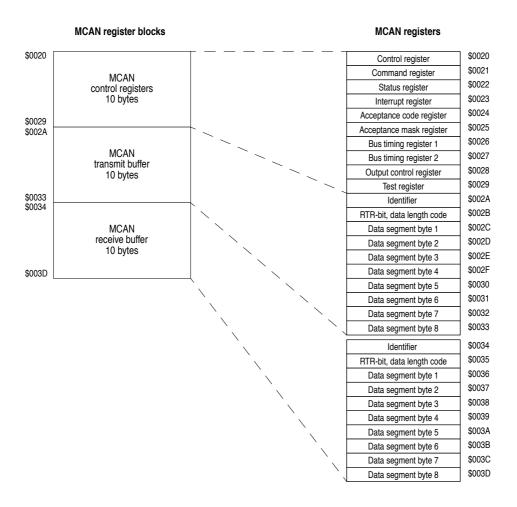

| A.2.2                      | Address allocation                                   |     |  |

| A.2.3                      | Control registers                                    |     |  |

| A.2.4                      | MCAN control register (CCNTRL)                       |     |  |

| A.2.5                      | MCAN command register (CCOM)                         |     |  |

| A.2.6                      | MCAN status register (CSTAT)                         |     |  |

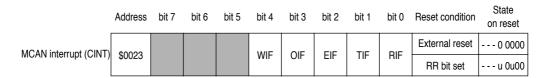

| A.2.7                      | MCAN interrupt register (CINT)                       |     |  |

| A.2.8                      | MCAN acceptance code register (CACC)                 |     |  |

| A.2.9                      | MCAN acceptance mask register (CACM)                 |     |  |

| A.2.10                     |                                                      |     |  |

| A.2.11                     | MCAN bus timing register 1 (CBT1)                    |     |  |

| A.2.12                     |                                                      |     |  |

| A.2.13                     |                                                      |     |  |

A.2.14

Remote transmission request and data length code register (TRTDL) ............ A-22

| Paragraph<br>Number | TABLE OF CONTENTS                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------------------|----------------|

| A.2.15              | Transmit data segment registers (TDS) 1 – 8                       | A-23           |

| A.2.16              | Receive buffer identifier register (RBI)                          |                |

| A.2.17              | Remote transmission request and data length code register (RRTDL) | A-23           |

| A.2.18              | Receive data segment registers (RDS) 1 – 8                        | A-23           |

| A.2.19              | Organization of buffers                                           | A-25           |

|                     | B<br>TOUCAN                                                       |                |

| D.4                 |                                                                   | D.4            |

|                     | Introduction                                                      |                |

|                     |                                                                   |                |

|                     | External Pins                                                     |                |

|                     | The CAN system                                                    |                |

|                     | Message buffer structure                                          |                |

|                     | Common fields to extended and standard format frames              |                |

| B.6.1               | CODE                                                              |                |

| B.6.2               | LENGTH (receive mode)                                             |                |

| B.6.3               | LENGTH (transmit mode)                                            |                |

| B.6.4               | DATA BYTE 0.7                                                     |                |

| B.6.5               | RESERVED                                                          |                |

|                     | Fields for extended format frames                                 |                |

| B.7.1               | TIME STAMP                                                        |                |

| B.7.2               | ID[28-18, 17-15]                                                  |                |

| B.7.3               | SRR — Substitute remote request                                   |                |

| B.7.4               |                                                                   |                |

| B.7.5<br>B.7.6      | ID[14-0]                                                          |                |

|                     | RTR — Remote transmission request                                 |                |

|                     | Fields for standard format frames                                 |                |

| B.8.1               | TIME STAMP                                                        |                |

| B.8.2               | ID[28-18]                                                         |                |

| B.8.3               | RTR — Remote transmission request                                 |                |

| B.8.4               | Functional overview                                               |                |

|                     |                                                                   |                |

|                     | Transmit process                                                  |                |

| B.11<br>B.11.1      | Receive process Self-received frames                              |                |

|                     |                                                                   |                |

| B.12.1              | Message buffer handling                                           |                |

| B.12.1              | Tx message buffer deactivation                                    |                |

|                     | Rx message buffer deactivation                                    |                |

|                     | Remote frames                                                     |                |

|                     |                                                                   |                |

|                     | Overload frames                                                   |                |

|                     | Time stamp                                                        |                |

|                     | Bit-timing operation notes                                        |                |

| D. 10               | Dit-uning operation notes                                         | 14-ط           |

vii

| Paragraph<br>Number | TABLE OF CONTENTS                                                                                                                        | Page<br>Numbe |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| B.19                | TOUCAN initialisation sequence                                                                                                           |               |

| B.20                | Special operating modes                                                                                                                  |               |

| B.20.1              | DEBUG mode                                                                                                                               |               |

| B.20.2              | STOP mode                                                                                                                                |               |

| B.20.2              |                                                                                                                                          |               |

| B.20.3              | Auto Power Save mode                                                                                                                     |               |

| B.20.4              | Support BERR for RISC architechture (BERR_PLUG)                                                                                          |               |

| B.20.4              |                                                                                                                                          |               |

| B.20.4              | · · · · · · · · · · · · · · · · · · ·                                                                                                    |               |

|                     | Interrupts (IDO DILLO 0)                                                                                                                 |               |

| B.21.1              | Modular family archtecture (IRQ_PLUG = 0)                                                                                                |               |

| B.21.2              | RISC family architecture (IRQ_PLUG = 1)                                                                                                  |               |

| B.22<br>B.22.1      | Programmer's model                                                                                                                       |               |

| B.22.1              | Programming validity                                                                                                                     |               |

| B.22.3              | System registers                                                                                                                         |               |

| B.22.4              | MCR — Module configuration register                                                                                                      |               |

| B.22.5              | TCR — Test configuration register                                                                                                        |               |

| B.22.6              | ICR — Interrupt configuration register (Modular family IRQ_PLUG = 0)                                                                     |               |

| B.22.7              | ICR — Interrupt configuration register (Modular family IRQ_1 200 = 0)  ICR — Interrupt configuration register (RISC family IRQ_PLUG = 1) |               |

|                     | Control registers                                                                                                                        |               |

| B.23.1              | CTRL0 — Control register 0                                                                                                               |               |

| B.23.2              | CTRL1 — Control register 1                                                                                                               |               |

| B.23.3              | PRESDIV — Prescaler divide register                                                                                                      |               |

| B.23.4              | CTRL2 — Control register 2                                                                                                               |               |

| B.23.5              | TIMER — Free running timer                                                                                                               |               |

| B.24                | Rx mask registers                                                                                                                        |               |

| B.24.1              | RXMASK — Rx global mask register                                                                                                         |               |

| B.24.2              | RX14MASK — Rx buffer 14 mask                                                                                                             |               |

| B.24.3              | RX15MASK — Rx buffer 15 mask                                                                                                             | B-37          |

| B.25                | Global information registers                                                                                                             | B-38          |

| B.25.1              | STATH, STATL — Error and status report registers                                                                                         |               |

| B.25.2              | IMASKH, IMASKL— Interrupt mask registers                                                                                                 |               |

| B.25.3              | IFLAGH, IFLAGL — Interrupt flag registers                                                                                                |               |

| B.25.4              | Error counters                                                                                                                           | B-42          |

|                     | C THE MOTOROLA COAL FARILE CAN (MCCANO) MORIULE                                                                                          |               |

|                     | THE MOTOROLA SCALEABLE CAN (MSCAN08) MODULE                                                                                              |               |

| C.1                 | Features                                                                                                                                 | C-1           |

| C.2                 | External Pins                                                                                                                            | C-3           |

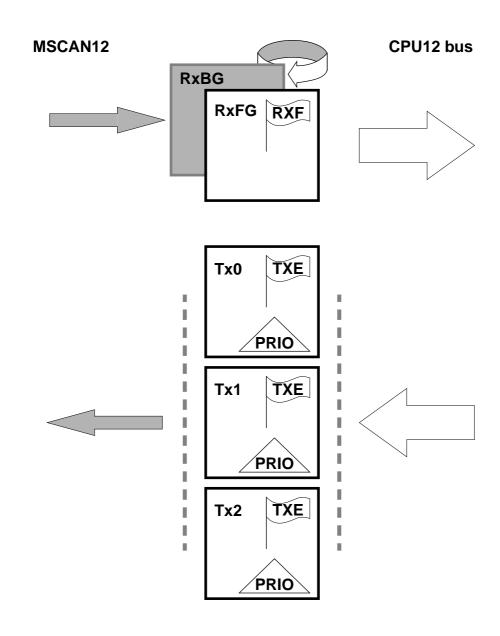

| C.3                 | Message Storage                                                                                                                          | C-4           |

| C.3.1               | Background                                                                                                                               | C-4           |

| C.3.2               | Receive Structures                                                                                                                       | C-5           |

| C.3.3               | Transmit Structures                                                                                                                      | C-7           |

| Paragraph<br>Number | TABLE OF CONTENTS                                  | Page<br>Numbe |

|---------------------|----------------------------------------------------|---------------|

|                     | Identifier acceptance Filter                       |               |

| C.5                 | Interrupts                                         |               |

| C.5.1               | Interrupt Acknowledge                              |               |

| C.5.2               | Interrupt Vectors                                  |               |

| C.6                 | Protocol Violation Protection                      |               |

|                     | Low Power Modes                                    |               |

| C.7.1               | MSCAN08 Internal Sleep Mode                        |               |

| C.7.2               | MSCAN08 Soft Reset Mode                            |               |

| C.7.3               | MSCAN08 Power Down Mode                            |               |

| C.7.4               | CPU Wait Mode                                      |               |

| C.7.5<br>C.8        | Programmable Wake-Up Function                      |               |

| C.8                 | Timer Link                                         |               |

|                     | Memory Map                                         |               |

|                     | Programmer's Model of message storage              |               |

| C.11.1              | Message Buffer Outline                             |               |

| C.11.2              | Identifier Registers (IDRn)                        |               |

| C.11.3              | Data Length Register (DLR)                         |               |

| C.11.4              | Data Segment Registers (DSRn)                      |               |

| C.11.5              | Transmit Buffer Priority Registers (TBPR)          |               |

| C.12                | Programmer's Model of Control Registers            |               |

| C.12.1              | Overview                                           |               |

| C.12.2              | MSCAN08 Module Control Register (CMCR0)            |               |

| C.12.3              | MSCAN08 Module Control Register (CMCR1)            |               |

| C.12.4              | MSCAN08 Bus Timing Register 0 (CBTR0)              |               |

| C.12.5              | MSCAN08 Bus Timing Register 1 (CBTR1)              |               |

| C.12.6              | MSCAN08 Receiver Flag Register (CRFLG)             |               |

| C.12.7              | MSCAN08 Receiver Interrupt Enable Register (CRIER) |               |

| C.12.8              | MSCAN08 Transmitter Flag Register (CTFLG)          |               |

| C.12.9              | MSCAN08 Transmitter Control Register (CTCR)        |               |

| C.12.1<br>C.12.1    |                                                    |               |

| C.12.1              | · · · · · · · · · · · · · · · · · · ·              |               |

| C.12.1              |                                                    |               |

| C.12.1              |                                                    |               |

|                     | D THE MOTOROLA SCALEABLE CAN (MSCAN12) MODUL       |               |

| D.1                 | Features                                           | D 1           |

| D.1<br>D.2          | External Pins                                      |               |

| D.2<br>D.3          | Message Storage                                    |               |

| D.3.1               | Background                                         |               |

| D.3.2               | Receive Structures                                 |               |

| D.3.3               | Transmit Structures                                |               |

| Paragrapl<br>Number | TABLE OF CONTENTS                                   | Page<br>Number |

|---------------------|-----------------------------------------------------|----------------|

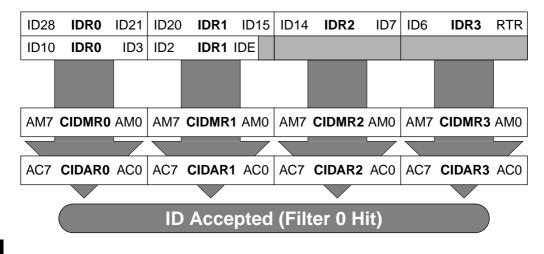

| D.4                 | Identifier Acceptance Filter                        | D-8            |

| D.5                 | Interrupts                                          |                |

| D.5.1               | Interrupt Acknowledge                               |                |

| D.5.2               | Interrupt Vectors                                   | D-12           |

| D.6                 | Protocol Violation Protection                       | D-12           |

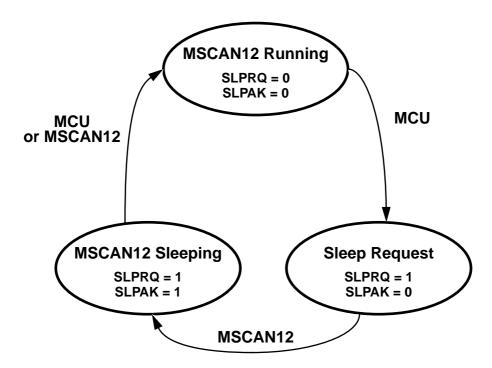

| D.7                 | Low Power Modes                                     | D-13           |

| D.7.1               | MSCAN12 Sleep Mode                                  | D-14           |

| D.7.2               | MSCAN12 Soft Reset Mode                             |                |

| D.7.3               | MSCAN12 Power Down Mode                             | D-15           |

| D.7.4               | Programmable Wake-Up Function                       | D-15           |

| D.8                 | Timer Link                                          | D-16           |

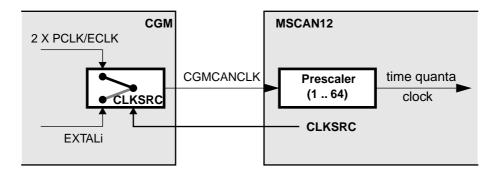

| D.9                 | Clock System                                        |                |

| D.10                | Memory Map                                          |                |

| D.11                | Programmer's Model of Message Storage               |                |

| D.11.1              | Message Buffer Outline                              |                |

| D.11.2              | 3 · · · · · · · · · · · · · · · · · · ·             |                |

| D.11.3              | - 5.15 5.15 ( 1.7)                                  |                |

| D.11.4              | Data Segment Registers (DSRn)                       |                |

| D.11.5              |                                                     |                |

|                     | Programmer's Model of Control Registers             |                |

| D.12.1              | Overview                                            |                |

| D.12.2              | MSCAN12 Module Control Register 0 (CMCR0)           |                |

| D.12.3              | MSCAN12 Module Control Register 1 (CMCR1)           |                |

| D.12.4              | MSCAN12 Bus Timing Register 0 (CBTR0)               |                |

| D.12.5              | MSCAN12 Bus Timing Register 1 (CBTR1)               |                |

| D.12.6              | MSCAN12 Receiver Flag Register (CRFLG)              |                |

| D.12.7              | 3                                                   |                |

| D.12.8              |                                                     |                |

| D.12.9              | MSCAN12 Transmitter Control Register (CTCR)         |                |

| D.12.1              |                                                     |                |

| D.12.1              | ,                                                   |                |

| D.12.1              | · · · · · · · · · · · · · · · · · · ·               |                |

| D.12.1              |                                                     |                |

| D.12.1              | 3                                                   |                |

| D.12.1              | /                                                   |                |

| D.12.1              |                                                     |                |

| D 12 1              | 7 MSCAN12 Port CAN Data Direction Register (DDRCAN) | 11-40          |

**GLOSSARY**

**INDEX**

# **LIST OF FIGURES**

| Figure<br>Number | TITLE                                                     | Page<br>Number |

|------------------|-----------------------------------------------------------|----------------|

| 2-1              | CAN layers                                                | 2-2            |

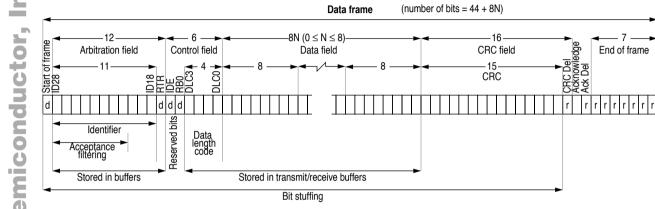

| 3-1              | Data frame                                                | 3-2            |

| 3-2              | Arbitration field                                         | 3-2            |

| 3-3              | Control field                                             | 3-3            |

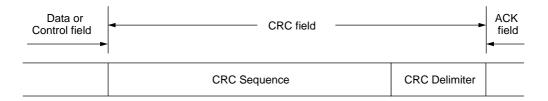

| 3-4              | CRC field                                                 | 3-4            |

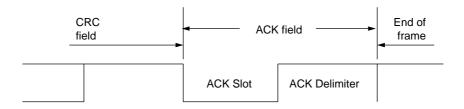

| 3-5              | ACK field                                                 | 3-5            |

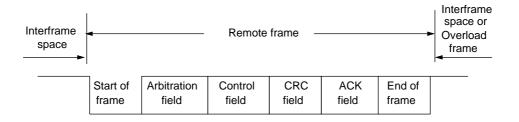

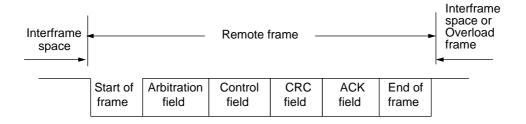

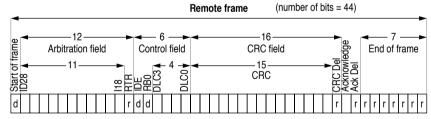

| 3-6              | Remote frame                                              | 3-6            |

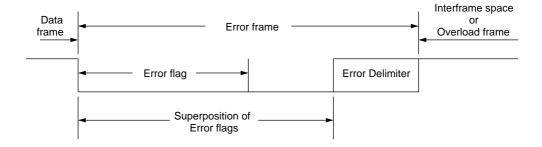

| 3-7              | Error frame                                               | 3-7            |

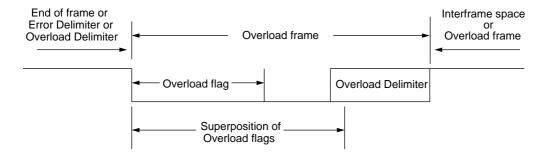

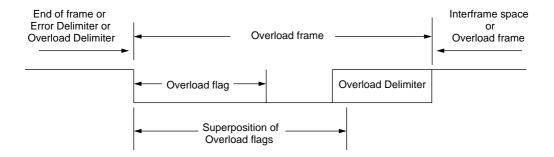

| 3-8              | Overload frame                                            | 3-8            |

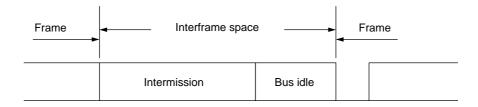

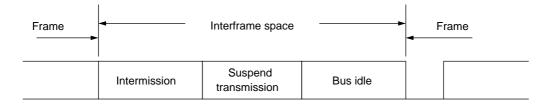

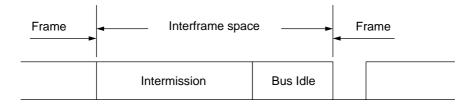

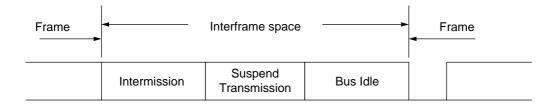

| 3-9              | Interframe space (1)                                      | 3-10           |

| 3-10             | Interframe space (2)                                      | 3-10           |

| 3-11             | CAN frame formats                                         |                |

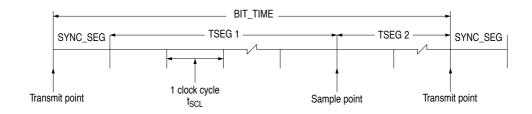

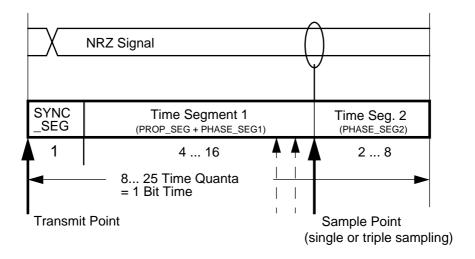

| 6-1              | Nominal bit time                                          | 6-1            |

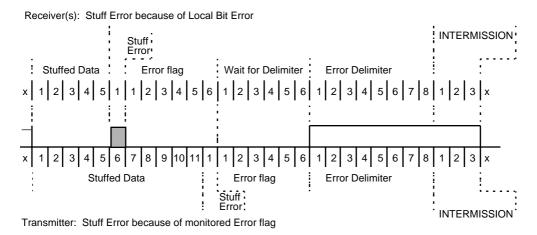

| 7-1              | Local error                                               |                |

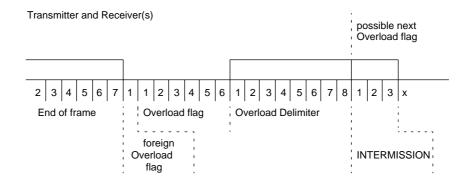

| 7-2              | Two consecutive Overload frames                           |                |

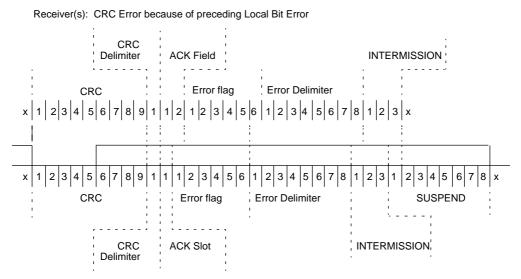

| 7-3              | Acknowledge error at transmitter, all nodes Error PASSIVE |                |

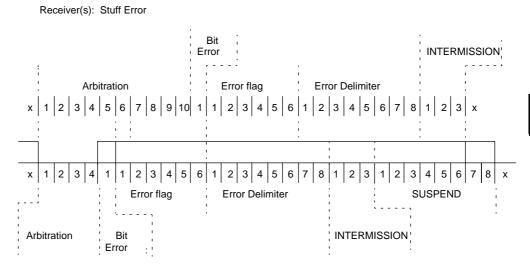

| 7-4              | Local error at transmitter, all nodes Error PASSIVE       |                |

| 7-5              | Bit timing for maximum oscillator tolerance               |                |

| 7-6              | Bit timing for maximum bit rate                           |                |

| 9-1              | CAN layers                                                |                |

| 10-1             | Data frame                                                |                |

| 10-2             | Arbitration field; Standard Format                        |                |

| 10-3             | Arbitration field; Extended Format                        |                |

| 10-4             | Control field; Standard Format and Extended Format        |                |

| 10-5             | CRC field                                                 |                |

| 10-6             | ACK field                                                 |                |

| 10-7             | Remote frame                                              |                |

| 10-8             | Error frame                                               |                |

| 10-9             | Overload frame                                            |                |

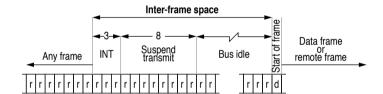

| 10-10            | Interframe space (1)                                      |                |

| 10-11            | Interframe space (2)                                      |                |

| 10-12            | CAN frame format - Standard Format                        |                |

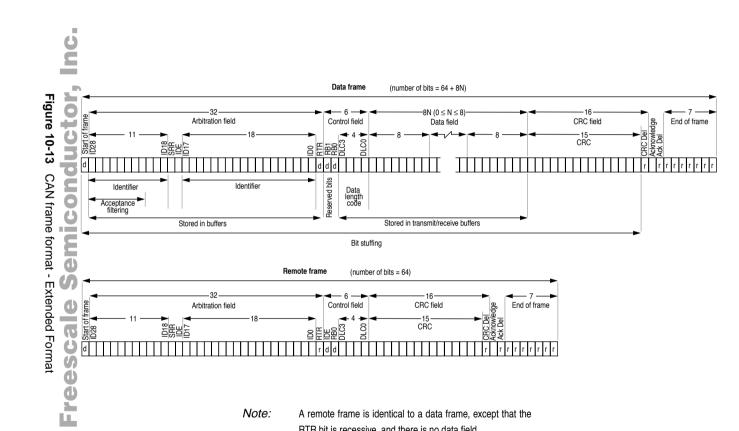

| 10-13            | CAN frame format - Extended Format                        | 10-16          |

| Figure<br>Number | TITLE                                                                | Page<br>Number |

|------------------|----------------------------------------------------------------------|----------------|

| 13-1             | Nominal bit time                                                     | 13-1           |

| 13-2             | Bit timing of CAN devices without local CPU                          | 13-3           |

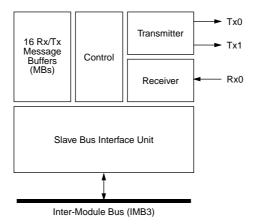

| A-1              | MCAN module block diagram                                            | A-2            |

| A-2              | Block diagram of the MCAN interface                                  | A-5            |

| A-3              | MCAN module memory map                                               | A-6            |

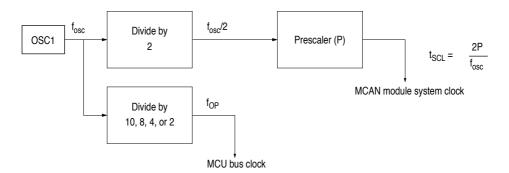

| A-4              | Oscillator block diagram                                             | A-16           |

| A-5              | Segments within the bit time                                         | A-17           |

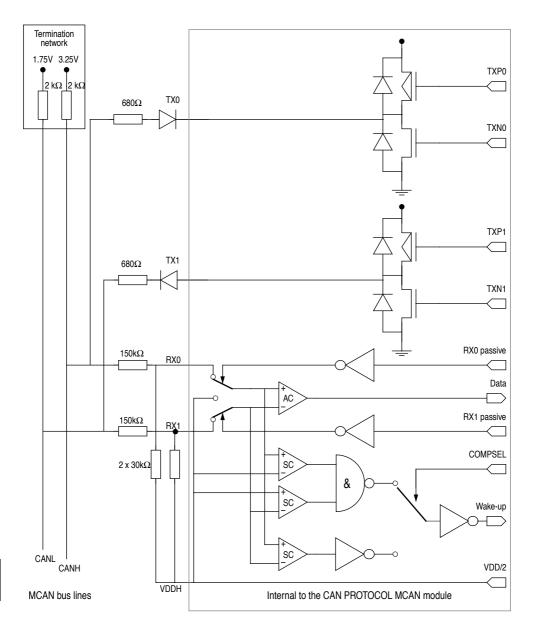

| A-6              | A typical physical interface between the MCAN and the MCAN bus lines | A-24           |

| B-1              | TOUCAN block diagram and pinout                                      | B-2            |

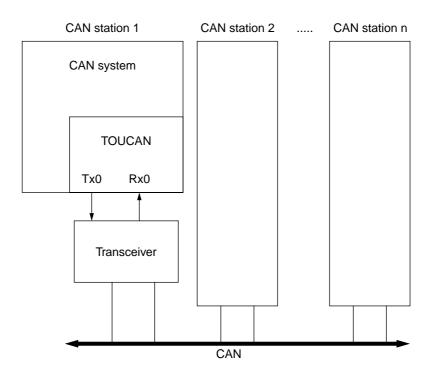

| B-2              | Typical CAN system                                                   | B-3            |

| B-3              | Message buffer structure                                             | B-4            |

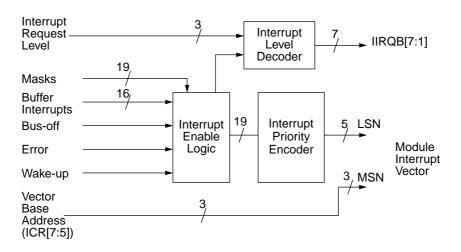

| B-4              | TOUCAN interrupt vector generation                                   | B-20           |

| B-6              | Int request multiplex timing                                         | B-22           |

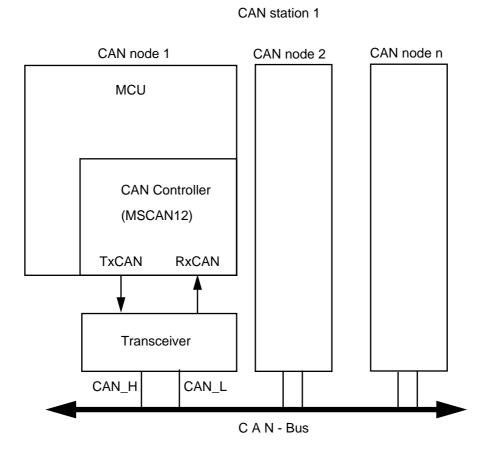

| C-1              | The CAN System                                                       | C-3            |

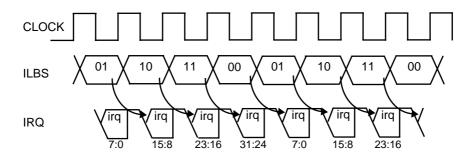

| C-2              | User Model for Message Buffer Organization                           |                |

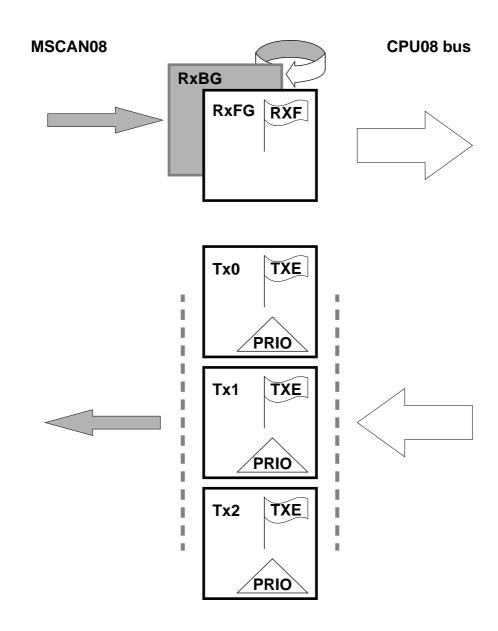

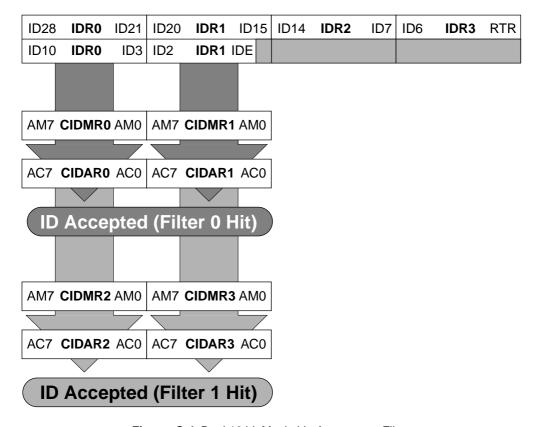

| C-3              | Single 32 bit Maskable Identifier Acceptance Filter                  |                |

| C-4              | Dual 16 bit Maskable Acceptance Filters                              |                |

| C-5              | Quadruple 8 bit Maskable Acceptance Filters                          |                |

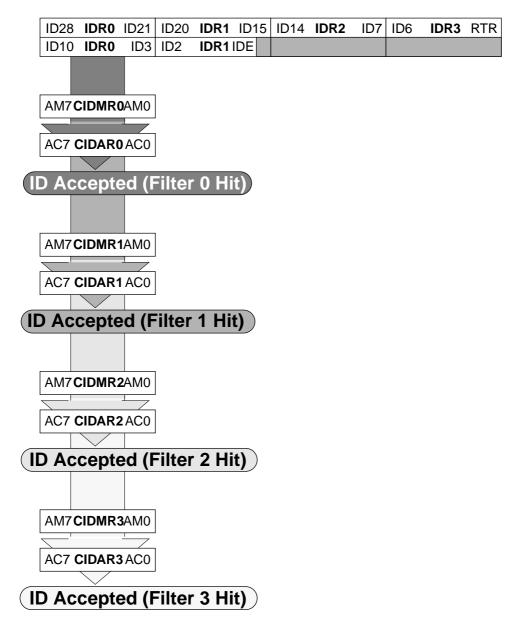

| C-6              | Sleep Request / Acknowledge Cycle                                    |                |

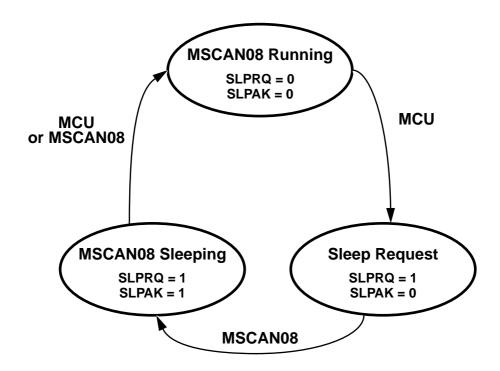

| C-7              | Clocking Scheme                                                      | C-17           |

| C-8              | Segments within the Bit Time                                         |                |

| C-9              | Receive/transmit message buffer extended identifier registers        |                |

| C-10             | Standard identifier mapping registers                                |                |

| D-1              | The CAN System                                                       | D-3            |

| D-2              | User model for message buffer organisation                           | D-6            |

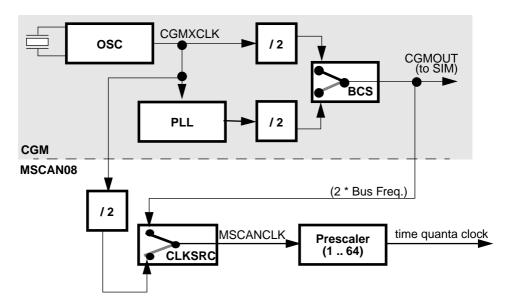

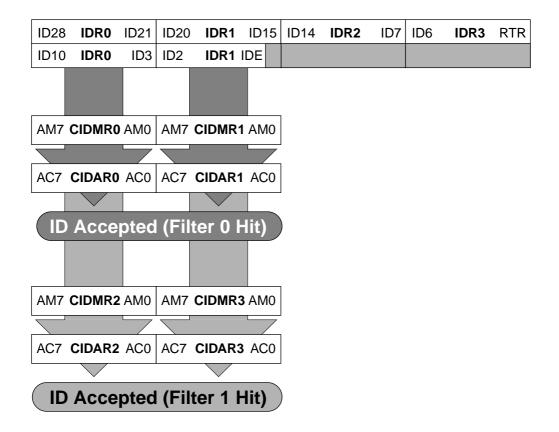

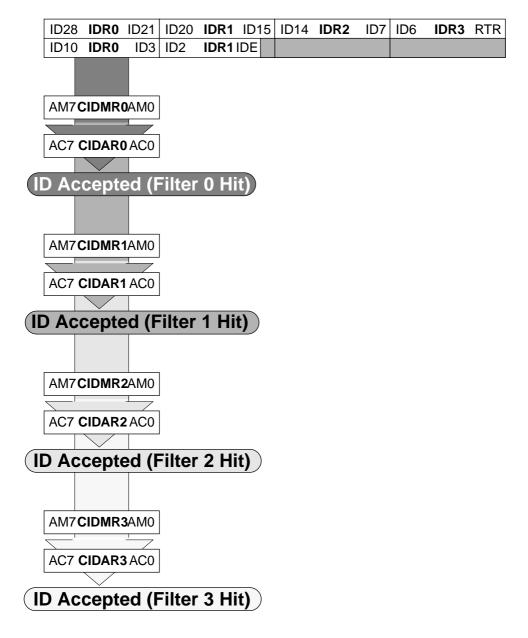

| D-3              | 32-bit Maskable Identifier Acceptance Filter                         | D-8            |

| D-4              | 16-bit Maskable Acceptance Filters                                   | D-9            |

| D-5              | 8-bit Maskable Acceptance Filters                                    | D-10           |

| D-6              | Sleep Request / Acknowledge Cycle                                    | D-14           |

| D-7              | Clocking Scheme                                                      | D-17           |

| D-8              | Segments within the Bit Time                                         | D-18           |

| D-9              | MSCAN12 Memory Map                                                   | D-19           |

| D-10             | Receive/transmit message buffer extended identifier                  | D-21           |

| D-11             | Standard identifier mapping                                          | D-21           |

| D-12             | Identifier acceptance registers (1 <sup>ST</sup> bank)               | D-38           |

| D-13             | Identifier acceptance registers (2 <sup>ND</sup> bank)               | D-38           |

| D-14             | Identifier mask registers (1 <sup>ST</sup> bank)                     | D-38           |

| D-15             | Identifier mask registers (2NDhank)                                  | D-30           |

Go to: www.freescale.com

# **LIST OF TABLES**

| 3-1         Data length coding         3-4           10-1         Data length coding         10-5           A-1         Control registers         A-7           A-2         Synchronization jump width         A-16           A-3         Baud rate prescaler         A-16           A-4         Time segment values         A-18           A-5         Output control modes         A-19           A-6         MCAN driver output levels         A-21           A-7         Data length codes         A-22           A-7         Data length codes         A-22           B-8         MCAN data buffers         A-25           B-1         Message buffer code for Rx buffers         B-5           B-2         Message buffer code for Tx buffers         B-5           B-3         Examples of system clock/CAN bit-rate/SCLOCK         B-14           B-4         Interrupt priorities and vector addresses         B-21           B-5         Interrupt levels         B-22           B-6         TOUCAN memory map         B-22           B-7         Interrupt levels         B-30           B-8         Configuration control of Tx0, Tx1 pins         B-30           B-9         Mask examples for normal/extende                                             | Table<br>Number | TITLE                                                                                                            | Page<br>Number |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|----------------|

| A-1       Control registers       A-7         A-2       Synchronization jump width       A-16         A-3       Baud rate prescaler       A-16         A-4       Time segment values       A-18         A-5       Output control modes       A-19         A-6       MCAN driver output levels       A-21         A-7       Data length codes       A-22         1-8       MCAN data buffers       A-25         B-1       Message buffer code for Rx buffers       B-5         B-2       Message buffer code for Tx buffers       B-5         B-3       Examples of system clock/CAN bit-rate/SCLOCK       B-14         B-4       Interrupt priorities and vector addresses       B-21         B-5       Interrupt levels       B-22         B-6       TOUCAN memory map       B-24         B-7       Interrupt levels       B-30         B-8       Configuration control of Tx0, Tx1 pins       B-32         B-9       Mask examples for normal/extended messages       B-36         B-10       Bit error status       B-38         B-11       Fault confinement sate of TOUCAN       B-40         C-1       MSCAN08 Interrupt Vectors       C-12         C-2       MS                                                                                                 | 3-1             | Data length coding                                                                                               | 3-4            |

| A-2         Synchronization jump width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-1            | Data length coding                                                                                               | 10-5           |

| A-3 Baud rate prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A-1             | Control registers                                                                                                | A-7            |

| A-4         Time segment values         A-18           A-5         Output control modes         A-19           A-6         MCAN driver output levels         A-21           A-7         Data length codes         A-22           1-8         MCAN data buffers         A-25           B-1         Message buffer code for Rx buffers         B-5           B-2         Message buffer code for Tx buffers         B-5           B-3         Examples of system clock/CAN bit-rate/SCLOCK         B-14           B-4         Interrupt priorities and vector addresses         B-21           B-5         Interrupt levels         B-22           B-6         TOUCAN memory map         B-24           B-7         Interrupt levels         B-30           B-8         Configuration control of Tx0, Tx1 pins         B-32           B-9         Mask examples for normal/extended messages         B-36           B-10         Bit error status         B-36           B-11         Fault confinement sate of TOUCAN         B-40           C-1         MSCAN08 Interrupt Vectors         C-12           C-2         MSCAN08 vs. CPU operating modes         C-13           C-3         CAN Standard Compliant Bit Time Segment Settings         C-18                  | A-2             | Synchronization jump width                                                                                       | A-16           |