# 4-Way Traffic Intersection Control

Christopher Thweatt, Joseph Asteefan, John Drabik, Madison Cornett

Photo By Christopher Evans/MediaNews Group/Boston Herald

Proof of Concept: To reduce the footprint and complexity of hardware necessary to prototype and install flexible traffic control systems.

- Traffic control simulation built in VHDL code:

- **Finite State Machine**  $\bigcirc$

- Counter 0

Introduction

- Decoder 0

- Serializer  $\bigcirc$

- Segment and LED Display 0

# Methodology

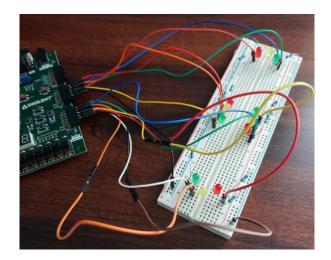

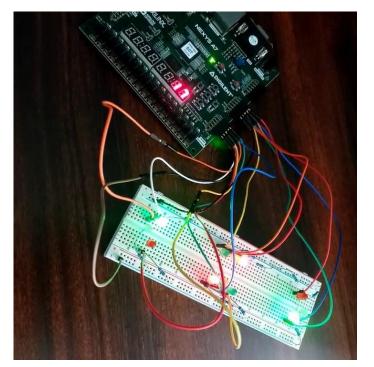

- Artix-A7 FPGA, bread board, and colored LEDs

- Integer counter

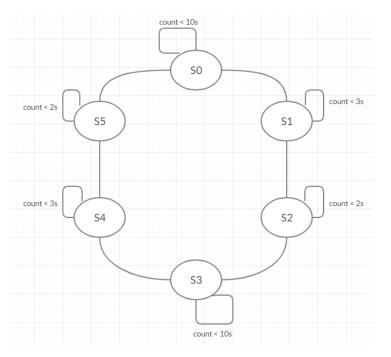

- State machine:

- Each state represents a different light sequence for each of the signals, and changes dependent on the accumulated count value.

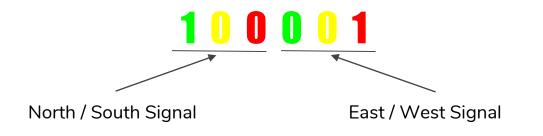

- Six bit output. Example: 100 (green) for the north/south signals and 001 (red) for the east/west signals.

#### **Top Level Design** clk resetn 🛶 6 "count" Q Integer Counter FSM Decoder 4 А В Serializer

8

8

0

#### Counter

```

library ieee;

1 1

use ieee.std logic 1164.all;

2

3

4 - entity counter is

5 ¦

port ( clock, resetn: in std logic;

6

Q: out integer range -1500000000 to 150000000);

7 🖂

end counter;

8 i

9 - architecture bhv of counter is

10

signal Qt: integer range -1500000000 to 1500000000;

11

12

begin

13

14 🖂

process (resetn, clock)

15

begin

16 🖂

if resetn = '0' then

17

Qt <= -1500000000;

18 ;

elsif (clock'event and clock='l') then

19 🖯

if Qt = 1500000000 then

20

Qt <= -1500000000;

21

else

22

Qt <= Qt + 1;

23 🖂

end if;

24 🖨

end if;

25 🖂

end process;

0 <= 0t;

26

27 \ominus end bhv;

```

- Initially used 0 to 30 counter

- Integer instead of BCD

#### **State Machine**

48 i

49 ⊖ 50 ¦ 51 ⊖ 52 ⊖ 53 ⊖ 54 ⊖

55 🔶 56 킂

57 🖂 58 칮

59 ( 60 ( 61 ( 62 ( 63 ( 64 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 ( 65 (

| 11 🖯 | architecture Behavioral of fsm is            |

|------|----------------------------------------------|

| 12   | type state_type is (s0, s1, s2, s3, s4, s5); |

| 13   | <pre>signal state: state_type;</pre>         |

|      | begin                                        |

| 15 넞 |                                              |

| 16   | begin                                        |

| 17 뒂 | if rstn = '0' then state <= s0;              |

| 18   | elsif (clk'event and clk = 'l') then         |

| 19 뒂 | case state is                                |

| 20 🖯 | when s0 =>                                   |

| 21 🖯 | if Q = -500000000 then state <= s1;          |

| 22   | else state <= s0;                            |

| 23 🖯 | end if;                                      |

| 24 뒂 | when sl =>                                   |

| 25 🖯 | if Q = -200000000 then state <= s2;          |

| 26   | else state <= sl;                            |

| 27 白 | end if;                                      |

| 28 🖯 | when s2 =>                                   |

| 29 🖯 | if Q = 0 then state <= s3;                   |

| 30   | else state <= s2;                            |

| 31 🖨 | end if;                                      |

| 32 🖯 | when s3 =>                                   |

| 33 🖯 | if Q = 1000000000 then state <= s4;          |

| 34   | else state <= s3;                            |

| 35 🏳 | end if;                                      |

| 36 🖯 | when s4 =>                                   |

| 37 🖯 | if Q = 1300000000 then state <= s5;          |

| 38   | else state <= s4;                            |

| 39 白 | end if;                                      |

| 40 뒂 | when s5 =>                                   |

| 41 🖯 | if Q = 1500000000 then state <= s0;          |

| 42   | else state <= s5;                            |

| 43 🖨 | end if;                                      |

| 44 🔶 | end case;                                    |

| 45 🖨 | end if;                                      |

| 46 🖂 | end process;                                 |

| A.2. |                                              |

|      |                                              |

| 100 is green, 010 is yellow, 001 is red |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|--|--|--|--|--|--|--|--|--|

| outputs: process(state)                 |  |  |  |  |  |  |  |  |  |

| begin                                   |  |  |  |  |  |  |  |  |  |

| case state is                           |  |  |  |  |  |  |  |  |  |

| when s0 => northeast <= "100001";       |  |  |  |  |  |  |  |  |  |

| southwest <= "100001";                  |  |  |  |  |  |  |  |  |  |

| when s1 => northeast <= "010001";       |  |  |  |  |  |  |  |  |  |

| southwest <= "010001";                  |  |  |  |  |  |  |  |  |  |

| when s2 => northeast <= "001001";       |  |  |  |  |  |  |  |  |  |

| southwest <= "001001";                  |  |  |  |  |  |  |  |  |  |

| when s3 => northeast <= "001100";       |  |  |  |  |  |  |  |  |  |

| southwest <= "001100";                  |  |  |  |  |  |  |  |  |  |

| when s4 => northeast <= "001010";       |  |  |  |  |  |  |  |  |  |

| southwest <= "001010";                  |  |  |  |  |  |  |  |  |  |

| when s5 => northeast <= "001001";       |  |  |  |  |  |  |  |  |  |

| southwest <= "001001";                  |  |  |  |  |  |  |  |  |  |

| end case;                               |  |  |  |  |  |  |  |  |  |

| end process;                            |  |  |  |  |  |  |  |  |  |

66 🔶 end Behavioral;

| North | /South | L | East/West |   |   | State      |

|-------|--------|---|-----------|---|---|------------|

| G     | Y      | R | G         | Υ | R |            |

| 1     | 0      | 0 | 0         | 0 | 1 | <b>S</b> 0 |

| 0     | 1      | 0 | 0         | 0 | 1 | S1         |

| 0     | 0      | 1 | 0         | 0 | 1 | <b>S</b> 2 |

| 0     | 0      | 1 | 1         | 0 | 0 | <b>S</b> 3 |

| 0     | 0      | 1 | 0         | 1 | 0 | <b>S</b> 4 |

| 0     | 0      | 1 | 0         | 0 | 1 | <b>S</b> 5 |

#### Serializer and Decoder

| 9 (⇒ ar<br>10 ¦ | rchitecture Behavioral of dec is                     | resetn = 0             | N                    |            |          |     |

|-----------------|------------------------------------------------------|------------------------|----------------------|------------|----------|-----|

|                 | egin                                                 |                        | A (4)                |            | 1        |     |

| 12 🖯            | process (Q)                                          | 50                     |                      |            |          |     |

| 13              | begin                                                | 50                     | Int to 4-bit         | 4-bit to 7 | CACG (7) |     |

| 14 🖯            | if Q < -1400000001 then A <= "0000"; B <= "0000";    | S < 0                  |                      | segments   |          | /   |

| 15              | elsif Q < -1300000001 then A <= "0001"; B <= "0000"; |                        | decoder B (4)        | decoder    |          |     |

| 16              | elsif Q < -1200000001 then A <= "0010"; B <= "0000"; |                        | 1                    | decoder    |          |     |

| 17              | elsif Q < -1100000001 then A <= "0011"; B <= "0000"; |                        |                      |            | 1        |     |

| 18              | elsif Q < -1000000001 then A <= "0100"; B <= "0000"; | +                      |                      |            |          |     |

| 19              | elsif Q < -900000001 then A <= "0101"; B <= "0000";  |                        |                      |            |          |     |

| 20              | elsif Q < -800000001 then A <= "0110"; B <= "0000";  |                        |                      |            |          |     |

| 21              | elsif Q < -700000001 then A <= "0111"; B <= "0000";  | <pre></pre>            |                      |            |          |     |

| 22              | elsif Q < -600000001 then A <= "1000"; B <= "0000";  |                        | resetn               |            |          |     |

| 23              | elsif Q < -500000001 then A <= "1001"; B <= "0000";  | Y                      |                      |            |          |     |

| 24              | elsif Q < -400000001 then A <= "0000"; B <= "0001";  | 1                      |                      |            |          |     |

| 25              | elsif Q < -300000001 then A <= "0001"; B <= "0001";  |                        | Counter z            |            |          |     |

| 26              | elsif Q < -200000001 then A <= "0010"; B <= "0001";  | S1                     | > (0.001s)           |            |          |     |

| 27              | elsif Q < -100000001 then A <= "0011"; B <= "0001";  | 51 🖤                   | > (0.0013)           |            |          | 0 ( |

| 28              | elsif Q < -000000001 then A <= "0100"; B <= "0001";  | S < 1                  |                      |            |          | A 7 |

| 29              | elsif Q < 099999999 then A <= "0101"; B <= "0001";   |                        |                      |            |          |     |

| 30              | elsif Q < 199999999 then A <= "0110"; B <= "0001";   |                        |                      |            |          |     |

| 31              | elsif Q < 299999999 then A <= "0111"; B <= "0001";   |                        |                      | 1-to-2     | X (2)    |     |

| 32              | elsif Q < 399999999 then A <= "1000"; B <= "0001";   | L                      |                      | decoder    |          |     |

| 33              | elsif Q < 499999999 then A <= "1001"; B <= "0001";   | × 1                    | resetn               | decoder    |          |     |

| 34              | elsif Q < 599999999 then A <= "0000"; B <= "0010";   |                        |                      |            | _        |     |

| 35              | elsif Q < 699999999 then A <= "0001"; B <= "0010";   | <pre>&lt; E &gt;</pre> | E S                  |            |          |     |

| 36              | elsif Q < 799999999 then A <= "0010"; B <= "0010";   |                        |                      |            |          |     |

| 37              | elsif Q < 899999999 then A <= "0011"; B <= "0010";   | Y                      | FINITE STATE MACHINE |            |          |     |

| 38              | elsif Q < 999999999 then A <= "0100"; B <= "0010";   | 1                      |                      |            |          |     |

| 39              | elsif Q < 1099999999 then A <= "0101"; B <= "0010";  | 1                      | >                    |            |          |     |

| 40              | elsif Q < 1199999999 then A <= "0110"; B <= "0010";  |                        |                      | -          |          |     |

| 41              | elsif Q < 1299999999 then A <= "0111"; B <= "0010";  |                        |                      |            |          |     |

| 42              | elsif Q < 1399999999 then A <= "1000"; B <= "0010";  |                        |                      |            |          |     |

| 43              | elsif Q < 1499999999 then A <= "1001"; B <= "0010";  |                        |                      |            |          |     |

| 44              | elsif Q < 1500000001 then A <= "0000"; B <= "0011";  |                        |                      |            |          |     |

| 45 😑            | end if;                                              |                        |                      |            |          |     |

| 46 🖨            | end process;                                         |                        |                      |            |          |     |

47 🔶 end Behavioral;

### **XDC file / Experimental Setup**

- Clock signal

- 7 segment display

- First 7 ports

- AN 0-7

- Buttons

- CPU reset

- Pmod headers JA and JB

- JA first 6 ports

- JB first 6 ports

- Breadboard

- Wires

- Resistors

- External LEDs

# Demo

https://drive.google.com/file/d/1 FN8xiAmwgKfuOerfLMHYy7eF kHJUG4fz/view?usp=sharing

# Conclusion

- Knowledge of VHDL programming and the use of a finite state machine

- Decoders, counters, and serializers

- Being able to apply prior knowledge and modify existing code to adapt to the situation.

- Learned how to use the different ports to connect to a breadboard

- Used previous knowledge of LEDs and the function of a breadboard to implement the function.

- Strengthened our abilities to solve problems even in the most unideal situations.