# ECE 2700 Final Project

By: Foster Caragay, Marko Wassef, Vincent Tran, Athanathios Bebawy

#### What is it?

Our circuit resembles the logic of digital safes. A combination is set, and to unlock the system the same combination must be entered.

The option to reset the combination is available if the system is unlocked, or the system can be relocked. This option is selected by the select switch.

The combination is selected by putting a switch high (with an assigned decimal value) and selecting the "next" button. As the 4 digit combination is entered the 7-segment display will show what digit in the combination you are setting. Ex; if you are setting the third digit of the combination, the 7-segment will show a 3.

Once a combination has been set, the system awaits an input from the user. The input process for unlocking the system is the same as that used to set the combination.

Upon entering the correct combination, the system will illuminate led0 and display a U on the 7 segment display.

If the wrong combination is entered, the system will display an E and at the next button press, allow you to try again.

The input values are selected by sw0-9 The next button is assigned to btnC The function select switch is assigned to sw15

# Video <u>https://youtu.be/LSA9jJgUTYc</u>

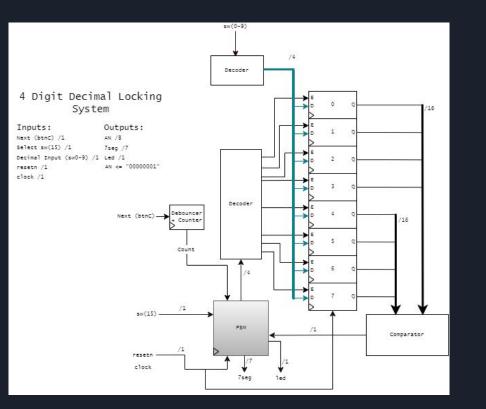

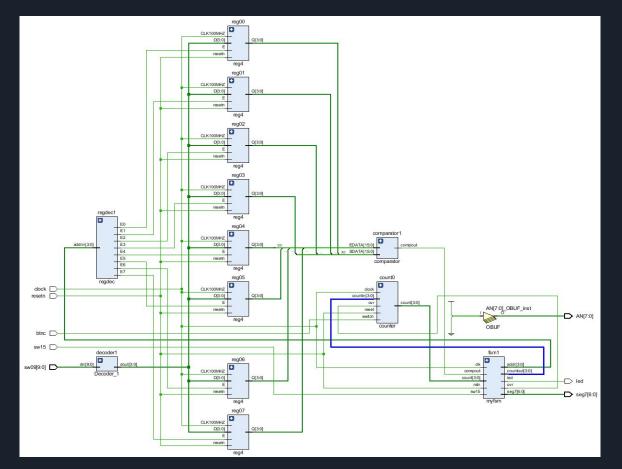

### Methodology - TOP Block Diagram/Datapath

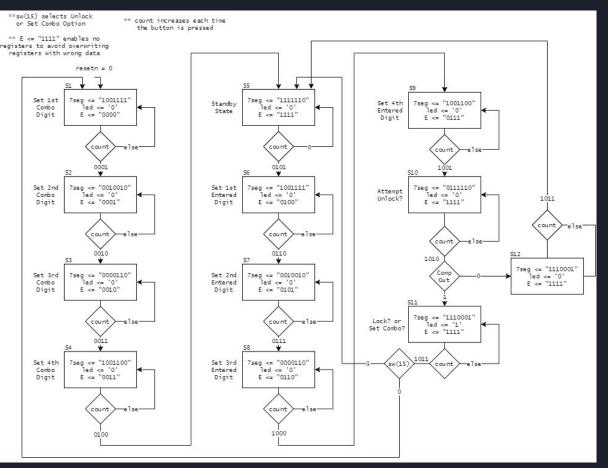

# Methodology - FSM/Control

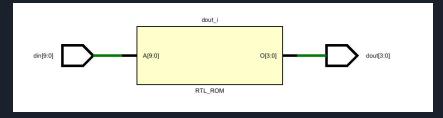

### 10 bit - 4 bit Decoder

|               |                  | 0.000 ns   |           |            |            |            |            |            |            |            |            |        |        |

|---------------|------------------|------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--------|--------|

| Name          | Value            | 0 ns       | 10 ns     | 20 ns      | 30 ns      | 40 ns      | 50 ns      | 60 ns      | 70 ns      | 80 ns      | 90 ns      | 100 ns | 110 ns |

| > 😼 din[9:0]  | 000000001 BINARY | 0000000001 | 000000010 | 0000000100 | 0000001000 | 0000010000 | 0000100000 | 0001000000 | 0010000000 | 0100000000 | 1000000000 | 00100: | 1000   |

| > 😻 dout[3:0] | 0 DECIMAL        | 0          | 1         | 2          | 3          | 4          | 5          | 6          | 7          | 8          | 9          | 0      |        |

|               |                  |            |           |            |            |            |            |            |            |            |            |        |        |

#### Example:

```

Input: "0000001000" = Output: "0111"

```

Input: "987654"210" = Output: Binary of bit that is high

#### \*Asynchronous

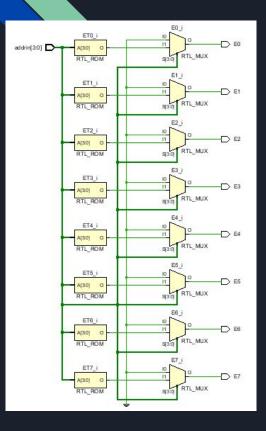

### Register Enable Decoder

|               |       | <mark>0.003 ns</mark> |           |           |           |       |                   |       |

|---------------|-------|-----------------------|-----------|-----------|-----------|-------|-------------------|-------|

| Name          | Value | 0 ns                  | 20 ns     | 40 ns     | 60 ns     | 80 ns | <sup>100 ns</sup> | 120 n |

| addrin[3:0]   | 0000  | 0000 0001             | 0010 0011 | 0100 0101 | 0110 0111 | K.    | 1111              |       |

| 14 E0         | 1     |                       |           |           |           |       |                   |       |

| 16 E1         | 0     |                       |           |           |           |       |                   |       |

| 14 E2         | 0     |                       |           |           |           |       |                   |       |

| 16 E3         | 0     |                       |           |           |           |       |                   |       |

| <b>a</b> E4   | 0     |                       |           |           | 3: 3:     |       |                   |       |

| 16 E5         | 0     |                       |           |           |           |       |                   |       |

| 1 <b>6</b> E6 | 0     |                       |           |           |           |       |                   |       |

| 16 E7         | 0     |                       |           |           |           |       |                   |       |

|               |       |                       |           |           |           |       |                   |       |

Example:

Addrin enables respective register in binary.

Addrin = "0010", enables register 2..

Addrin = "1111", disables all registers to prevent overwrites

#### \*Asynchronous

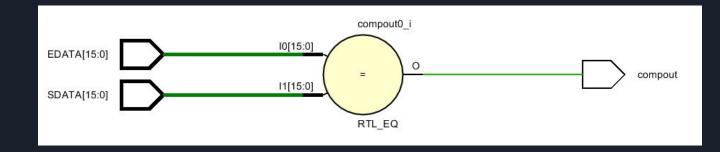

### Comparator

|                 |                  | <mark>0.000 ns</mark> |                 |         |            |                                         |       |       |       |  |

|-----------------|------------------|-----------------------|-----------------|---------|------------|-----------------------------------------|-------|-------|-------|--|

| Name            | Value            | 0 ns                  | <sup>5 ns</sup> | 10 ns   | 15 ns      | 20 ns                                   | 25 ns | 30 ns | 35 ns |  |

| > 😻 EDATA[15:0] | 0011001000100001 | 0011001               | 000100001       | 0010001 | .000100001 | 000000000000000000000000000000000000000 |       |       |       |  |

| > 😻 SDATA[15:0] | 0010001010100001 | 0010001               | 010100001       | 0010001 | .000100001 | 000000000000000000000000000000000000000 |       |       |       |  |

| 1 compout       | 0                |                       |                 |         |            |                                         |       |       |       |  |

Example:

If EDATA = SDATA then compout = '1' else compout = '0' end if;

\*Asynchronous

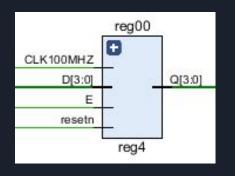

### 4 bit Register

#### Example:

On rising edge of clock, if E = '1' load D => Q If resetn = '0' Q => "0000".

\*Synchronous

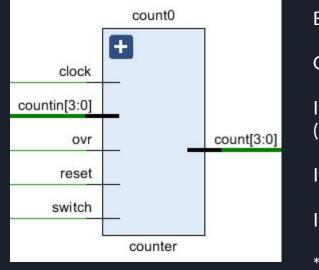

# Debouncer/Counter

#### Example:

On rising edge of clock, count a "pulse".

If switch is high, it must remain high for X amount of clock cycles (pulses) until count is iterated.

If ovr is high, overwrite the current count with, countin.

If reset is low, reset the system.

\*Synchronous

#### Experimental Setup

Criteria for experimental setup:

- Evaluation of individual components and functions

- Evaluation of the entire system

- Test edge cases

In order to verify the individual components, we tested each component with test data generated by a test bench.

In order to verify the functionality of the entire system we tested the top level functionality of the system with test data generated by a test bench.