# **Matrix Multiplication**

The architecture of 3x3 Matrix Multiplication for unsigned numbers.

List of Authors (Genbela Lifo, Nour Alnounou, Maryam Yaqo, Maryam Zadoyan) Electrical and Computer Engineering Department School of Engineering and Computer Science Oakland University, Rochester, MI

e-mails: lifo@oakland.edu, nalnounou@oakland.edu, maryamyaqo@oakland.edu, maryamzadoyan@oakland.edu

Abstract- The purpose of this project was to implement the architecture of a three-by-three multiplexer for unsigned numbers through VHDL. This design only utilizes the Nexys A7-100T board and a regular Keyboard. This project requested different coding techniques to complete the architecture of the circuit.

### I. INTRODUCTION

The goal of this VHDL project is to create and implement a synthesizable matrix multiplier that can calculate 3x3 matrices in size. The report outline shows the strategy of the architectural design, the implementation, and the ultimate outcomes. The architecture of the matrix multiplexer was implemented via VHDL in the Xilinx Vivado Design. We used an external keyboard as the system's input, which is connected through a USB port to the Nexys A7-100T board. The board was programmed to turn the 8-bit input from the keyboard into a 4-bit input to complete the 3x3. After the signal goes through the matrix process it is converted from Hex to a 7-segment decoder which after will display the results on the FPGA board.

#### II. METHODOLOGY

The purpose of this project is to be able to give an input that goes through the architecture of the 3x3 matrix multiplicator in order to display the same number as the input but into the 7-segment display in the Nexys A7-100T board. The methodology of this project consists of the matrix multiplication, block diagram, state diagram, and implementation of FPGA, where all of these parts and the inner steps will complete the structure of the 3x3 matrix multiplication architecture.

### A. MATRIX MULTIPLICATION

The matrix multiplication needed for this project follows the same steps as a normal math matrix multiplication but in this case, signals are replacing the numbers. Being able to multiply matrices is essential for comprehending how to use the circuit's various parts. The first rule is that the first matrix's columns must have the same number of rows as the second matrix's rows in order for matrices to be multiplied. This project focuses on 3x3 matrix multiplication, the example of this matrix using the letter component is shown in Figure 1[2].

Figure 1: Matrix Multiplication

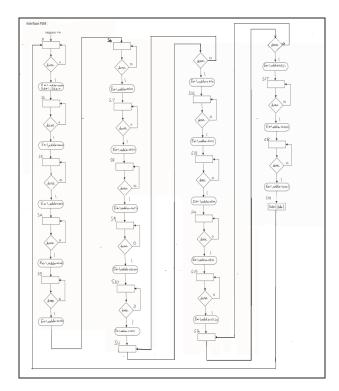

### B. STATE DIAGRAM

This is our Finite state machine. First We start with the first state and after we get the data from the keyboard we will receive this done. The first enable for the decoder will be one and the address will be zero (five bits), but the enable for the D-flip flop will be one and the done will be zero. It is zero because the data is not ready yet. Then it will go to the second state and we will get one for the enabled decoder and one for the address. From state two we will go to state three and get one for the enabled decoder and the address will be one. From state three it will go to the fourth state. We will get one for the enabled decoder and two for the address. Then it will go to the fifth state and we will get the enable decoder to be one and the address will be three. From this state, we will go to the sixth state and will get one for the enabled decoder and four for the address. Then we will go to the next stage which is the seventh state and will get one for the enabled decoder and five for the address. From the seventh state, we will go to

the eighth state and will get one for the enabled decoder and six for the address. Next, we will go to the ninth state and will get one for the enabled decoder and seven for the address. From state nine we will go to the tenth state and will get one for the enabled decoder and eight for the address. Then we will go to the eleventh state and will get one for the enabled decoder and nine for the address. From the eleventh state, we will go to the twelfth state and will get one for the enabled decoder and ten for the address. From that state, we will go to the thirteenth state and get one for the enabled decoder and eleven for the address. From that state, we will go to the fourteenth state. We will get one for the decoder and twelve for the address. From that state, we will go to state fifteen and will get one for the enabled decoder and thirteen for the address. From state fifteen we will go to state sixteen and will get one for the enabled decoder and fourteen for the address. From state sixteen we will go to state seventeenth and get one for the enabled decoder and fifteen for the address. From state seventeen we will go to state eighteen and get one for the to enable and sixteen for the address. From state eighteen we will go to the last state which is state nineteen. We will get one for the enabled D-flip flop and will get one for the done which means the data is ready now. In the end, we will go back to the first state.

Figure 2: FSM Diagram

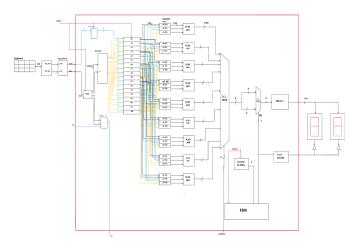

# C. CIRCUIT DESIGN

The picture below shows the complete circuit for this project. It is quite a complicated circuit that requires many components like two Decoders, a Register, Multipliers, Muxes, FSM, and more.

Figure 3: Circuit Diagram

The first part of the circuit starts with the keyboard which provides the input. The data will move to the first decoder which uses axi code to convert the data to 4 bits. This data will be stored in the registers. After Done is received from the keyboard the FSM will make sure that the right data will be represented. So it will display the results one by one and this is stored in the second decoder and from the decoder to the register. After this entire process is done the d flip flop will turn the LED on to show that the data is received. There are a total of 18 elements stored in the register, 9 per each matrix and all of them are 4 bits each. After the matrix multiplication is complete now each element will be 8-bit. This data now will be entering the Mux which controls the output we see from the matrix multiplication using switches. The last part of the circuit is the serializer [1] which includes the necessary components that the board knows to output the results in the two 7-segment displays.

## III. EXPERIMENTAL SETUP

We worked in the Vivado VHDL programming environment to build the code as well as simulated it in order to make sure that all the components of the circuit were working as expected. Separate source files were created for each component and later on combined on the top file to complete all the necessary connections between components.

| Mux.vhd × tb_top  | 1.vhd × decoder2. | /hd × tb_top | 1_behav.wcfg | x        |       |      |          |          |          |          |          |          |          | 1       |

|-------------------|-------------------|--------------|--------------|----------|-------|------|----------|----------|----------|----------|----------|----------|----------|---------|

| ର 📓 କ୍ କ୍         | X I N N           | 12 2 4       | [e   e[      | Н        |       |      |          |          |          |          |          |          |          |         |

|                   |                   |              | 1,280.010 ns |          |       |      |          |          |          |          |          |          |          |         |

| Name              | Value             |              | 1,200 ms     | 1,290 ns | 1,300 | ns   | 1,310 ns | 1,320 ns | 1,330 ns | 1,340 ns | 1,350 ns | 1,360 ns | 1,370 ns | 1,380 ; |

| V dock            | 0                 |              |              |          |       |      |          |          |          |          |          |          |          |         |

| V resetn          | 1                 |              |              |          |       |      |          |          |          |          |          |          |          |         |

| V done            | 0                 |              |              |          |       |      |          |          |          |          |          |          |          |         |

| > ♥ Dout[7:0]     | 22                |              | 22           |          |       |      |          |          |          |          |          |          |          |         |

| > ♥ switches[3:0] | 0                 | 8            | 1            |          |       | 2    |          |          |          |          |          |          |          |         |

| V dn              | 1                 |              |              |          |       |      |          |          |          |          |          |          |          |         |

| > © x[7:0]        | 1e                | Sa           | 1e           | 18       | 18 12 |      | 54       | 45       | 36       | 8a.      | 72       | X        | 5a       |         |

| ) ♥ ca_cg(&0)     | 0110000           | 0001000      | 0110100      | 0001001  | 00    | 100  | 0100100  | 1001100  | 0000110  | 010300   | 0101111  |          | 0100100  |         |

| > 🖬 leds[60]      | 1001111           | 1110111      | 1001111      | 1111111  | 110   | 010  | 1011011  | 0110011  | 1111001  | 1111111  | 1110000  |          | 1011011  |         |

| > ₩ segs[6d]      | 0110000           | 0001000      | 0110100      | 0101001  | 100   | 100  | 0100100  | 1001100  | 0000110  | 010300   | 0101111  |          | 0100100  |         |

| > ♥ ar(7:0)       | 254               |              | 254          |          |       | 251  |          |          |          |          |          |          |          |         |

| > ♥ omu(3:0)      | 1110              | 1010         | 1110         | 100      | 0010  | 0101 | 0101     | 0100     | 0011     | 1010     | 0111     |          | 0101     |         |

|                   | 0                 |              |              |          |       |      |          |          |          |          |          |          |          |         |

|                   | 10000 ps          |              |              |          |       |      |          | 100      | 0 ps     |          |          |          |          |         |

|                   |                   |              |              |          |       |      |          |          |          |          |          |          |          |         |

Figure 4: Simulation

## IV. RESULTS

Overall the board functioned as desired and the right results were displayed. The keyboard was able to provide the inputs and the LED turned on after all the data was received and later saved in the register. Very quickly as expected the 7-segment display showed the right results after the switches selected which element of the results to display.

### CONCLUSIONS

This was a successful project. We were able to complete all the basic requirements. As in every case, there is always room for improvement or challenging steps that can be added to the project for example the ability to work with signed numbers or improving the concept of the project so the user doesn't need to choose which displays they want to see by using the witches on the board but maybe the keyboard as well. The options are endless but overall this project was challenging and it showed vicarious results.

#### References

[1] D.Llamocca's Unit 7 serializer example project.

https://moodle.oakland.edu/pluginfile.php/784 6520/mod\_resource/content/17/Notes%20-%2 0Unit%207.pdf

[2] Threads: Basic Theory and Libraries. (n.d.).

Retrieved December 4, 2022, from users.cs.cf.ac.uk website: https://users.cs.cf.ac.uk/Dave.Marshall/C/node

29.html

[3] Laxman, S., et al. "FPGA implementation of different multiplier architectures." *International Journal of Emerging Technology and Advanced Engineering* 2.6 (2012): 292-295.

[4] Bhairannawar, Satish S., et al. "Efficient FPGA Based Matrix Multiplication Using Mux and Vedic Multiplier." *International Journal of Computers and technology* 12.5 (2014).