# 4 Way Traffic Light Controller

ECE 2700: Professor Daniel Llamocca

Sam Narusch, Richard Pinto, Christina Salama, Adrian Sinishtaj

#### Introduction

In this project, we designed and implemented a 4 way traffic light controller.

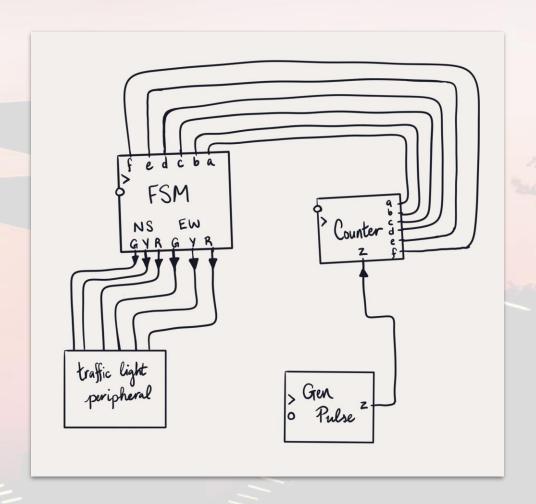

Consists of an FSM (Finite State Machine), a counter, and a gen pulse that display signals on an external board with LED's.

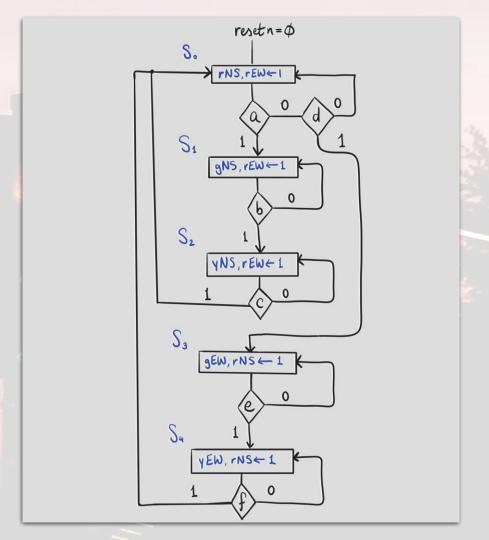

The simulated intersection has 8 seconds with the green light, 4 seconds with yellow light.

All lights will be red for an additional 2 seconds concurrently for safety purposes.

# **Block Diagram**

## **FSM Diagram**

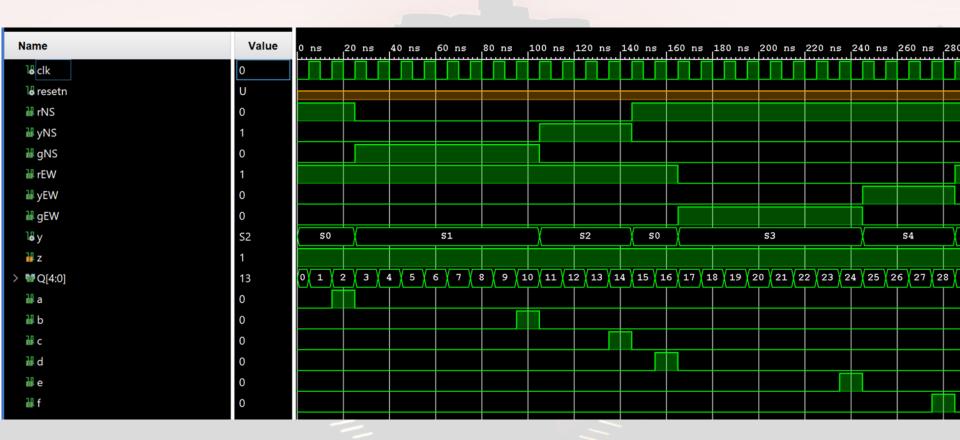

### **Simulation**

#### **VHDL Code for Finite State Machine**

```

entity fsm is

port (clock, resetn: in std logic;

a, b, c, d, e, f : in std logic;

rNS, yNS, gNS, rEW, yEW, gEW: out std logic);

e,d,resetc: out std logic);

--done: out std logic);

27 \(\hatcharpoonup \) end fsm:

28

--struct is architecture name and can call it whatever you want as long as its the same for end 'struct'

architecture struct of fsm is

31

type state is (S0, S1, S2, S3, S4);

32

signal v:state;

33

34

begin

--VHDL is concurrent, so order of f, x, and y do not matter

50 A end if:

36 ⊟

Transitions: process (resetn, clock, a, b, c, d, e, f)

51 ← end process;

37

begin

Outputs: process (v)

38 🖯

if resetn = '0' then

begin

39

v<=S0: --initial state

54

--resetC<='0': d<='0':: --default values

40

elsif (clock'event and clock='1') then

55 !

rNS <= '0'; vNS <= '0'; aNS <= '0'; rEW <= '0'; vEW <= '0'; aEW <= '0';

41 □

case v is

56 E

case v is

42 E

when S0 \Rightarrow if a \Rightarrow '1' then y \iff S1;

57 '

when S0 => rNS <= '1'; rEW <= '1'; --if RL = '1' then resetC <= '1';

43

elsif d = '1' then y \le S3; else y \le S0;

58

when S1 => qNS <= '1'; rEW <= '1'; --if GL = '1' then resetC <= '1';

end if:

59

45

when S1 \Rightarrow if b = 'l' then v \leq S2; else v \leq S1; end if;

60

when S3 => aEW <= '1'; rNS <= '1'; --if GL = '1' then resetC <= '1';

46

when S2 => if c = '1' then y \le S0; else y \le S2; end if;

when S4 => vEW <= '1': rNS <= '1': --e <= '1': d <= '0': if YL ='1'

47

when S3 \Rightarrow if e = 'l' then v \leq S4; else v \leq S3; end if;

62 ← end case;

48

when S4 \Rightarrow if f = '1' then v \leq S0; else v \leq S4; end if;

63 (a) end process;

49 🗀

end case:

64

65 ← end struct:

```

#### **VHDL Code for Counter**

```

use IEEE.STD LOGIC 1164.ALL;

use ieee.std logic arith.all;

entity counter is

port ( clock, resetn, z: in std logic;

Q: out std logic vector (3 downto 0);

a, b, c, d, e, f: out std logic);

end counter;

10 :

architecture Behavioral of counter is

signal Qt: integer range 0 to 28;

13

begin

14 !

15 ⊖

process (resetn, clock, z)

16 '

begin

17 ⊖

if resetn = '0' then

18

Ot <= 0;

elsif (clock'event and clock = 'l') and z = 'l' then

19 :

```

```

if Ot = 28 then

Qt <= 0;

else

24

Qt <= Qt + 1;

25 (

end if:

26 (

end if:

end process;

Q <= conv std logic vector(Qt,4);

29

30 .

a <= '1' when Qt = 2 else '0';

31

b <= '1' when Qt = 10 else '0';

32

c <= '1' when Ot = 14 else '0':

33

d <= '1' when Qt = 16 else '0';

34

e <= '1' when Ot = 24 else '0':

35

f <= '1' when Qt = 28 else '0';

36

end Behavioral:

```

## **VHDL Code for Genpulse**

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use ieee.std logic unsigned.all;

use ieee.std logic arith.all;

use ieee.math real.log2;

use ieee.math real.ceil;

17

entity my genpulse is

19

generic (COUNT: INTEGER:= (10**8)/2); -- (10**8)/2 cycles of T = 10 ns --> 0.5 s

port (clock, resetn, EN: in std logic;

Q: out std logic vector ( integer(ceil(log2(real(COUNT)))) - 1 downto 0);

z: out std logic);

30 □

end my genpulse;

31 :

begin

24

32 E

architecture Behavioral of my genpulse is

33

constant nbits: INTEGER:= integer(ceil(log2(real(COUNT))));

26

34

signal Qt: std logic vector (nbits -1 downto 0);

35 €

begin

36 🖨

29

```

```

process (resetn, clock)

if resetn = '0' then

Qt <= (others => '0');

elsif (clock'event and clock = '1') then

if EN = 'l' then

if Qt = conv std logic vector (COUNT-1, nbits) then

Qt <= (others => '0');

38

else

39

Qt <= Qt + conv std logic vector (1, nbits);

40 (

end if:

41 0

end if:

42 A

end if:

43 🖨

end process;

44 :

45 :

z <= '1' when Qt = conv std logic vector (COUNT-1, nbits) else '0';

46

0 <= Ot:

47

end Behavioral;

```

## **VHDL Code for Top File**

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

```

use IEEE.STD LOGIC ARITH.ALL;

use IEEE.STD LOGIC UNSIGNED.ALL;

use ieee.math real.log2;

use ieee.math real.ceil;

entity top is

port( resetn, clk : in std logic;

qNS, qEW, vNS, vEW, rNS, rEW : out std logic);

end top;

12

architecture struct of top is

component fsm

28 - component my genpulse

port (clock, resetn: in std logic;

generic (COUNT: INTEGER:= (10**8)/2); -- (10**8)/2 cycles of T = 10 ns --> 0.5 s

a, b, c, d, e, f : in std logic;

30

port (clock, resetn, EN: in std logic;

rNS, yNS, gNS, rEW, yEW, gEW: out std logic);

Q: out std logic vector ( integer(ceil(log2(real(COUNT)))) - 1 downto 0);

31

end component;

32

z: out std logic);

33 (

end component;

component counter

signal a, b, c, d, e, f, z : std_logic;

port ( clock, resetn, z: in std logic;

35

Q: out std logic vector (3 downto 0);

36

begin

a, b, c, d, e, f: out std logic);

37

26 \(\hatcharpoone\) end component;

al: fsm port map (clock => clk, resetn=>resetn,

39

rNS => rNS, yNS => yNS, gNS => gNS, rEW => rEW,

40

yEW => yEW, gEW => gEW,

41 🖨

a \Rightarrow a, b \Rightarrow b, c \Rightarrow c, d \Rightarrow d, e \Rightarrow e, f \Rightarrow f);

a2: counter port map (clock => clk, resetn => resetn, a => a, b => b, c => c, d => d, e => e, f => f, q => open, z => z);

--z <= '1'; -- only for simulations

a3: my_genpulse port map (clock => clk, resetn => resetn, EN => '1', Q => open, z => z);

```

46 @ END STRUCT;

## **VHDL Code for Testbench**

```

9 D ENTITY top tb IS

10 @ END top tb;

11

ARCHITECTURE behavior OF top tb IS

13

14

-- Component Declaration for the Unit Under Test (UUT)

15 :

16 🖨

COMPONENT top

17 !

Port (resetn, clk : in std logic;

18

gNS, gEW, yNS, yEW, rNS, rEW : out std logic

19

):

clock process: process

20 (

END COMPONENT;

39

begin

21

40 !

clk <= '0'; wait for 5 ns;

signal clk, resetn : std logic;

clk <= 'l'; wait for 5 ns;

signal gNS, gEW, yNS, yEW, rNS, rEW : std logic;

42 🖯

end process;

25

BEGIN

43

26 1

44 '

-- Stimulus process

27

-- Instantiate the Unit Under Test (UUT)

stim proc: process

28 ⊕

uut: top PORT MAP (

46

begin

29

clk => clk,

-- hold reset state for 100 ns.

30

resetn => resetn,

31

gNS => gNS,

48

wait for 100 ns:

32

gEW => gEW,

49 □

--resetn <= '1':

33

yNS => yNS,

50 A

-- insert stimulus here

34

yEW => yEW,

51

wait;

35

rNS => rNS,

52

end process;

rEW => rEW);

36 (-)

53 @ END;

```