## INSTRUMENT TUNER

MICHAEL BOWERS, ESSMAT ALMUFTI, DANI YAKOUB, MARYAM SUBHI

ECE 2700 DIGITAL LOGIC DESIGN

#### DESCRIPTION

Our circuit is an instrument tuner that identifies and displays the musical note being played into it from an external source.

Two Parts:

External circuit

Digital Circuit

#### BACKGROUND

In Western musical notation there are a total of 12 notes, each set at a specific pitch according to a pitch standard (A440)

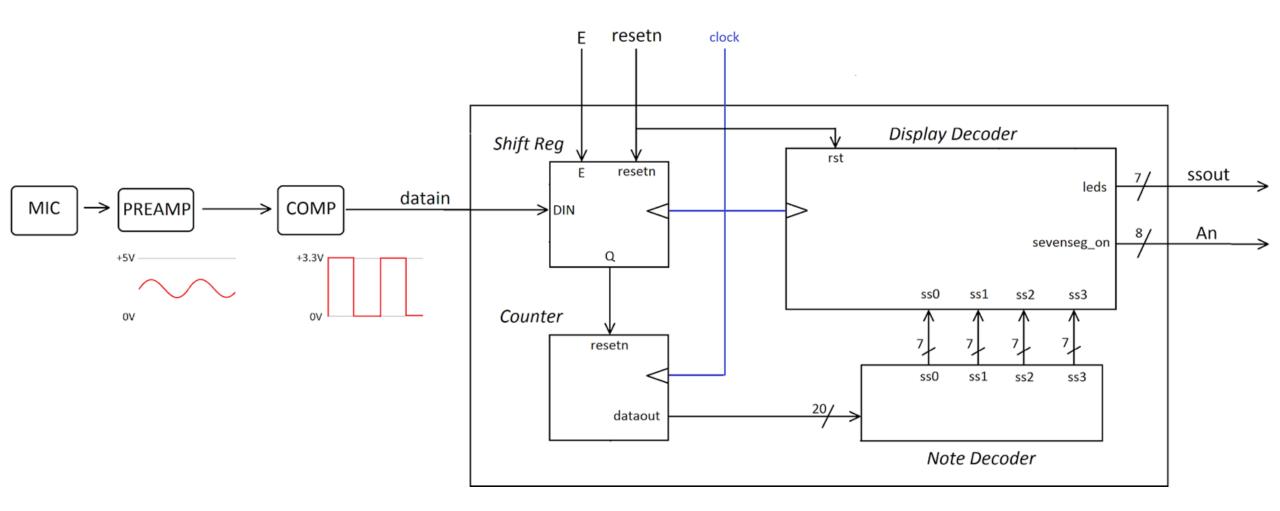

## Circuit (Block Diagram)

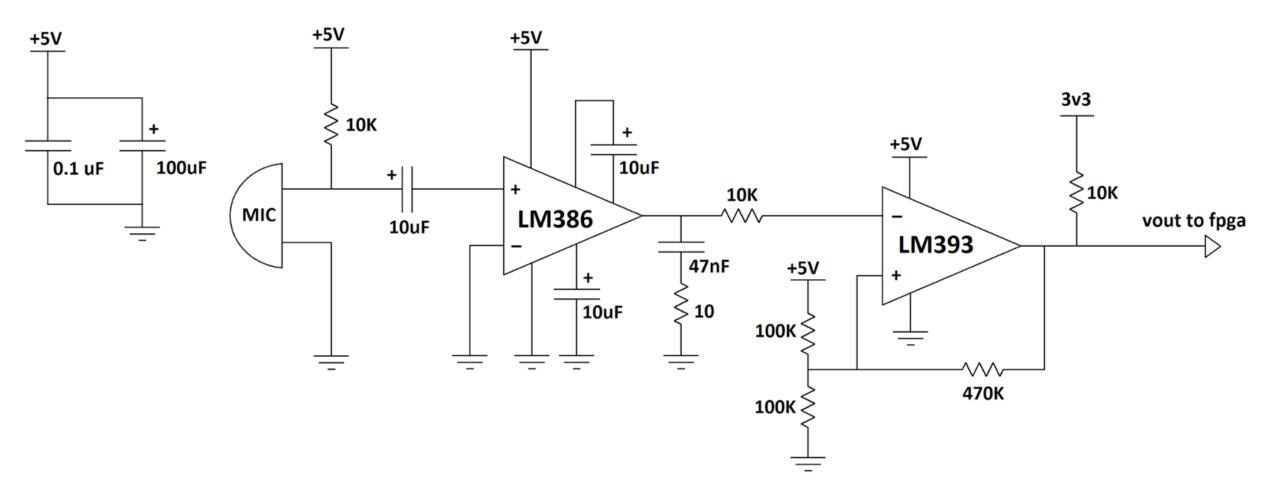

#### **External Circuit**

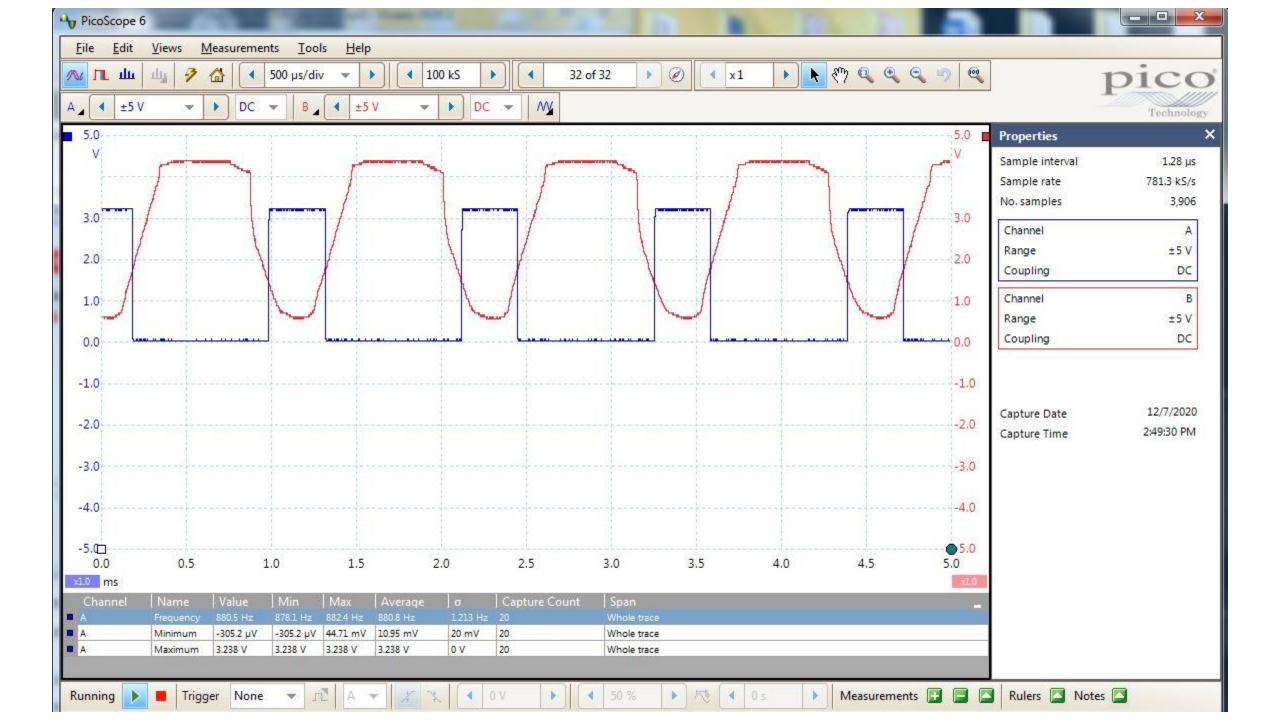

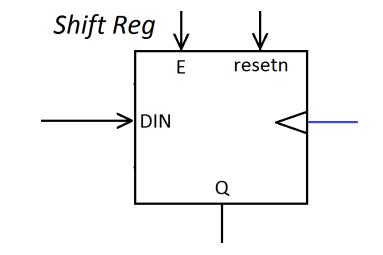

## SHIFT REGISTER

- 2-bit shift register

- datain carries the input wave

- Output Q signifies that the wave has been "registered"

| MSB | LSB | Q |

|-----|-----|---|

| 0   | 0   | 0 |

| 0   | 1   | 0 |

| 1   | 0   | 1 |

| 1   | 1   | 0 |

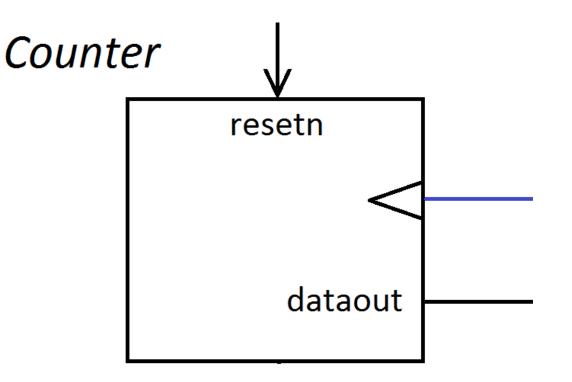

# COUNTER

- Add 1 to count 'n' for every clock event (rising edge).

- Q from the shift register acts as a reset for the counter, which outputs the final count and sets the count back to zero.

### **NOTE DECODER**

#### Final count = datain = 50MHz / (Freq. in Herz)

| Note/Condition       | Frequency Range (Hz) | Final Count Range |  |  |  |

|----------------------|----------------------|-------------------|--|--|--|

| E4                   | 328.688 to 330.592   | 152119 to 151244  |  |  |  |

| In Between E4 and F4 | 330.592 to 348.232   | 151243 to 143583  |  |  |  |

| F4                   | 348.232 to 350.252   | 143582 to 142754  |  |  |  |

| Note (Constition         | Dian 0 | Dian 1 | Dian 2 | Dian 2 | 7   |        | $\uparrow$ | $\uparrow$ |      | _   |

|--------------------------|--------|--------|--------|--------|-----|--------|------------|------------|------|-----|

| Note/Condition           | Disp 0 | Disp 1 | Disp 2 | Disp 3 | _   |        | 7          | 7          | 7    | 1   |

| Bb4                      |        |        | "B"    | "b"    |     |        | <br>ss0    | ss1        | ss2  | ss3 |

| In Between Bb4<br>and B4 | "B"    | "b"    | "_"    | "B"    | 20/ | datain |            | 001        | 332  | 555 |

| B4                       |        |        |        | "B"    |     | aatam  |            |            |      |     |

|                          |        |        |        |        |     |        | No         | te Dec     | oder |     |

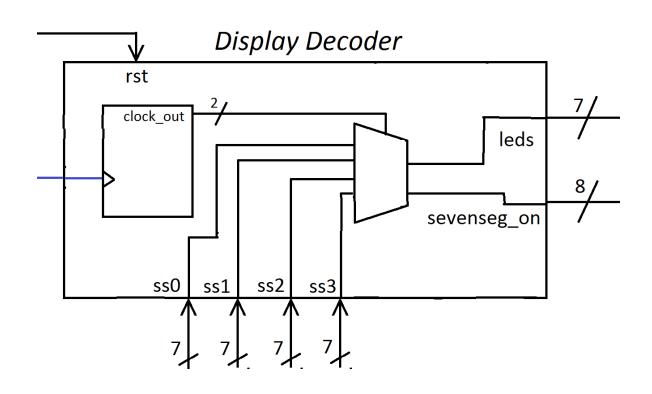

### **DISPLAY CONSIDERATIONS**

- Out from the note decoder are four std\_logic\_vector outputs intended for four 7-seg displays, but on the Nexys 4/DDR only one 7-seg configuration can be displayed at a time, so we have to implement a data selector/7-seg serializer.

- 7-seg has limited amount of potential states

- Due to this, we are using "9" to display a G note, an "8" for a B note, etc.

#### **DISPLAY DECODER**

- -Implemented as a 7-seg serializer

- -Internal clock divider

- -Internal data selector

#### DEMO

https://youtu.be/yW7LucIZ39Q

## CONCLUSIONS