## BINARY LOVE

THE STORY OF TWO LONELY STICK FIGURES IN A FPGA WORLD

CARLA GERST, XIANGYUAN GUO, KELLEY HARRIS, XINYANG JIAN

#### INTRODUCTION

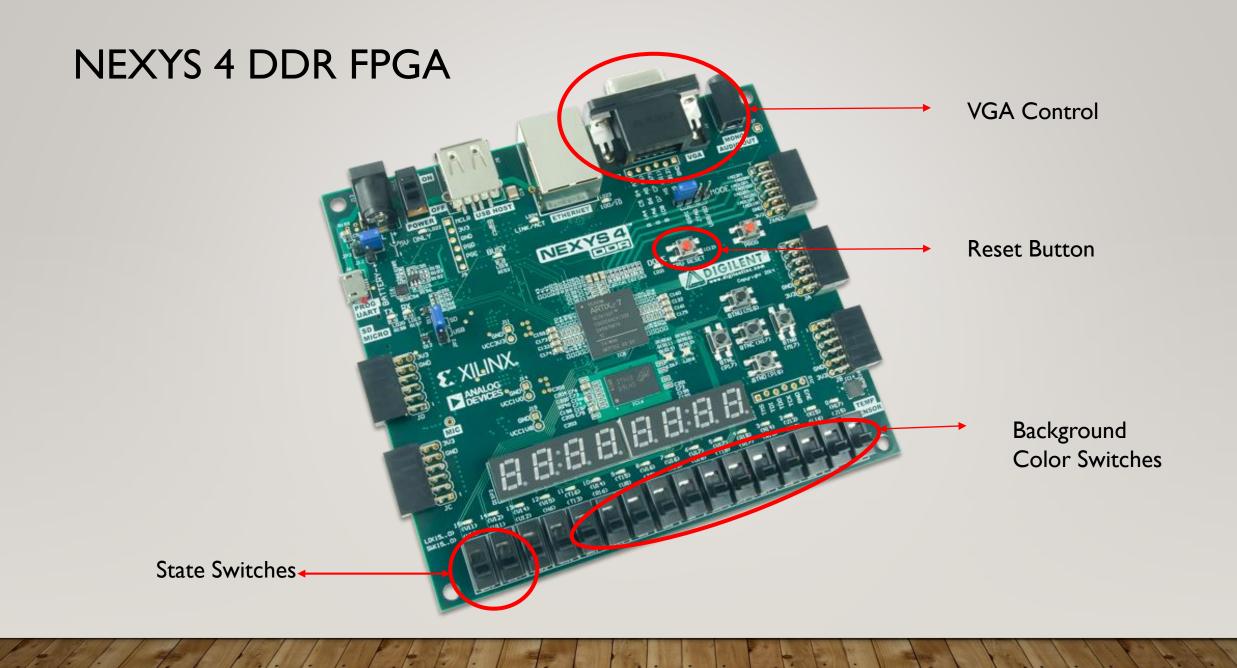

The purpose of this project was to create a program that allowed the user to mask specific pixel ranges which will hide certain parts of a single image at different times throughout the story. The story is told by manually adjusting the switches on the Nexys4 board.

#### **MATLAB**

MATLAB was used to convert the PNG image into usable text file.

```

clear all; close all; clc;

I = imread ('binarylove.png'); % RGB image

figure; imshow(I);

% Resizing the image to 256x256:

IP = imresize(I, [256 256]);

figure; imshow (IP);

% 24-bit RGB image: we will convert it to a 12-bit RGB image:

\Box for i = 1:3

IN(:,:,i) = IP(:,:,i)/16; % every plane converted to 4 bits. right shift

-end

figure; imshow(IN*16); % This is just so that 'imshow' can display the image properly

% Converting to text file. Format: 0|R|G|B in hexadecimal

q = quantizer ('ufixed', 'round', 'saturate', [4 0]);

textfile = 'myimg.txt';

fid = fopen (textfile, 'wt'); % generates text file in write mode

\neg for i = 1:256

for j = 1:256

R = IN(i,j,1); G = IN(i,j,2); B = IN(i,j,3);

Rh = num2hex(q, double(R)); Gh = num2hex(q, double(G)); Bh = num2hex(q, double(B));

fprintf(fid, '0%s%s%s\n',Rh, Gh, Bh);

end

end

fclose (fid);

```

### **VGA CONTROLLER & FSM**

Once the text file was created, it was then imported onto the VGA controller of the FPGA board. This was done using the provided VGA control program located on the class website.

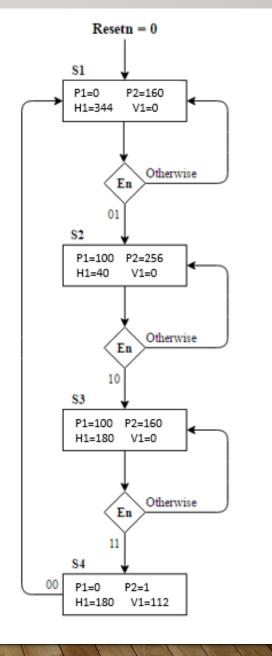

A Finite State Machine (FSM) was created using the Xilinx program. The state diagram is shown on the right.

#### Datapath Circuit

```

architecture Behavioral of FSM_cover is

32

33

type state is (S1, S2, S3, S4);

FSM CODE

signal y: state;

35

36

37

begin

38

Transitions: process (resetn, clock, en)

39

40

41

if resetn - '0' then -- asynchronous signal

42

y <- S1; -- if resetn asserted, go to initial state: S1

43

elsif (clock'event and clock - 'l') then

case y is

when S1 ->

if en - "01" then y<-S2; else y<-S1; end if;

48

if en - "10" then y<-S3; else y<-S2; end if;

50

if en - "11" then y<-S4; else y<-S3; end if;

51

52

if en - "00" then y<-S1; else y<-S4; end if;

end case;

53

end if;

54

55

end process;

Outputs: process (y)

59

case y is

60

when S1 -> p1 <- "0000000000", p2 <- "0010100000", h1 <- "0101011000", v1 <- "0000000000", -- 0/160

61

when $2 -> pl <- "0001100100", p2 <- "0100000000", h1 <- "0000101000", v1 <- "00000000000", --100/256

62

when S3 -> p1 <- "0001100100"; p2 <- "0010100000"; h1 <- "0010110100"; v1 <- "00000000000"; --100/160

63

when $4 -> p1 <- "00000000000"; p2 <- "00000000001"; h1 <- "0010110100"; v1 <- "0001110000"; --none

end case;

```

end process;

#### CHANGES TO PROVIDED VGA CODE

```

iram: in RAM generic map (NDATA => NDATA, FILE IMG => FILE IMG)

101

port map (clock, resetn, inRAM idata, inRAM add, inRAM we, inRAM en, inRAM odata);

102

103

-- Writing to this RAM is disabled here, but we can always enable to load new data

104

105

inRAM idata <= (others => '0'); inRAM en <= '1'; inRAM we <= '0';

106

107

-- The following formulas only works if the image is square and the width size is a power of 2.

108

109

inRAM_int <= (conv_integer(vcount_buf)-conv_integer(v1))*256+ (conv_integer(hcount_buf)-conv_integer(h1));</pre>

110

inRAM_add <=conv_std_logic_vector(inRAM_int, 16);

111

112

113

-- This is how we control what appears on the screen (only a square 2**NBPR x 2**NBPR)

sel_RGB <= '1' when (h1 < heount buf and heount buf < 2**NBPR+h1) and (v1< vcount buf and vcount buf < 2**NBPR+v1) else '0';

114

115

116

in RGB <= X"FFF" when (p1 < hcount buf and hcount buf < p2) else inRAM odata (11 downto 0);

117

118

with sel RGB select

119

in_RGB2 <= in_RGB when '1', -- only the 12 LSBs contain useful data

120

sw when others;

```

# Enjoy the STORY!

Boy: It's lonely being a single bit in this FPGA world. No one to walk through AND gates, OR gates. I've never even seen an XOR gate. I wonder if I'll ever find another bit to move through this integrated circuit.

Girl: I walk around wondering if I'll ever meet another bit. Even moving in an address bus to a multiplexer, there's no one to count on.

Narrator: One day, the girl bit gets on the address bus, and sees that she's not alone. She decides to use the shift register to move next to the boy.

Girl: "Hey, boy, I like your gray code".

Boy: "Sequence detected. Would you like to go through the XOR gate with me?

Narrator: Binary Love is like an asynchronous circuit. Eventually, your circuit will get implemented. AWE!