# DIGITAL LOGIC DESIGN VHDL Coding for FPGAs Unit 9

#### **✓ MISCELANEOUS TOPICS**

- I/O text files for simulation and synthesis. Example: serial multiplier, basic NI-to-NO LUT, VGA.

- Using Xilinx primitives: BRAMs, XADC, FIFOs, MMCMs, DSPs.

### ✓ I/O textfiles: Simulation

Reconfigurable Computing Research Laboratory

#### • Reading/Writing text files for Simulation:

- Unsigned iterative multiplier: Digital Library→Arithmetic Cores: (code).

- Testbench: tb\_mult\_iter.vhd. Input text file: in\_benchN12M8.txt

- Stimulus process: reads file line by line and place data on the inputs.

```

library ieee;

use ieee.std logic 1164.all;

use std.textio.all;

use ieee.std logic textio.all;

entity tb mult iter is

generic (N: INTEGER:= 12;

done

M: INTEGER:= 8);

Sequential

Multiplier

end tb mult iter;

stim: process

file IN FILE: TEXT open READ MODE is "in benchN12M8.txt";

variable BUFI: line;

variable VAR: std logic vector (N+M-1 downto 0);

begin

wait for 100 ns; resetn <= '1'; -- required for primitives

1 tb: loop

exit 1 tb when endfile(IN FILE);

readline (IN FILE, BUFI);

read (BUFI, var); -- read binary data. Use hread for hexadecimal data

dA \le var (N+M-1 downto M) ; dB \le var (M-1 downto 0) ;

s <= '1'; wait for T; s <= '0'; wait for T*(M+2); -- wait before the next start

end loop;

wait;

end process;

```

## ✓ I/O textfiles: Simulation

Reconfigurable Computing Research Laboratory

#### Reading/Writing text files for Simulation:

- Multiplier: Data input: A: 12 bits, B: 8 bits. Data output: P: 20 bits.

- Output capture process: It captures output data and writes on file line by line. Most circuits include a 'done' signal: at the rising clock edge, data is retrieved.

- Vivado:

- Include the input text file as a Simulation Source in the Project.

- The output text file will be written in sim/sim\_1/behav.

# ✓ I/O textfiles: Synthesis

Reconfigurable Computing Research Laboratory

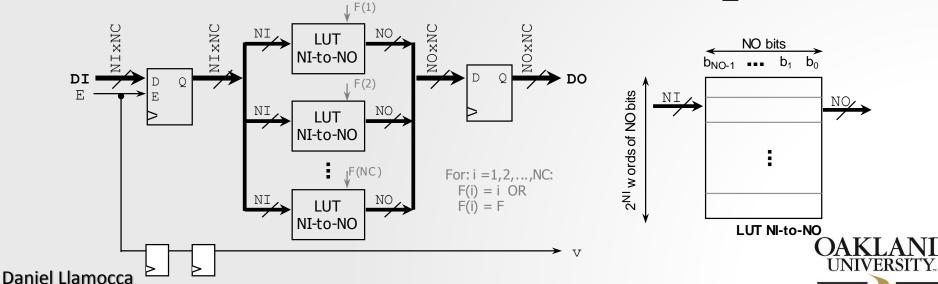

- Reading text files for Synthesis: LUT WITH I/O REGISTERS

- LUTsys.zip:

```

test.vhd, LUT_group.vhd, LUT_NItoNO.vhd, dffe.vhd, atb_test.vhd, LUT_values {NI} to {NO}.txt (this text file has to be in the same folder as LUT_NItoNO.vhd).

```

- LUT\_group: NC NI-to-NO LUTs. We can load each LUT NI-to-NO with: a different function (1 to NC), or the same function (specified by F).

- LUT\_NITONO: NI-to-NO LUT. It selects an NO-bit output word based on the NI-bit input. The LUT contents are read from an input text file.

- Vivado: Include the input text file(s) for testbenches as Simulation Sources. Output text file(s) will be written in /sim/sim\_1/behav.

# ✓ I/O textfiles: Synthesis

Reconfigurable Computing Research Laboratory

#### Reading text files for Synthesis:

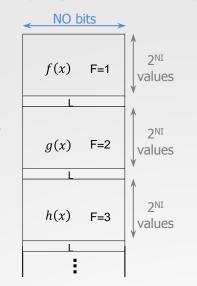

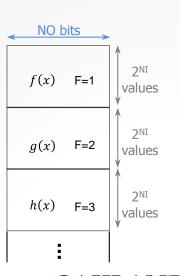

- Text File: LUT\_values{NI}to{NO}.txt.

This file holds 2<sup>NI</sup> NO-bit words for each function, separated by a line. Do not leave this line blank (we use an `L' character), otherwise *readline* will skip it and read the next line). This is the approach followed in this example for F=1,2,3,4,5.

- For a given function (F: 1,2,...), we start at line:  $(F-1)\times(2^{NI}+1)+1$ .

$$(F-1) \times (2^{NI}) + 1$$

.

## ✓ I/O textfiles: Synthesis

with constant inputs

Reconfigurable Computing Research Laboratory

- Reading text files for Synthesis: LUT values {NI} to {NO}.txt

- VHDL code:

```

architecture structure of LUT NItoNO is

Depending on the function, we start at

a different place in the text file

constant START POINTER: INTEGER:= (F-1)*(2**NI + 1) + 1;

type chunk is array (2**NI -1 downto 0) of std logic vector (NO-1 downto 0);

impure function ReadfromFile (FileName: in string; P: in integer) return chunk is

FILE IN FILE

: text open read mode is FileName

variable BUFF : line;

variable val : chunk;

begin

if P /= 1 then

To start at the proper

for j in 1 to P-1 loop

Text File is read with this function.

place in the text file, we

impure qualifier required when

readline (IN FILE, BUFF);

read P-1 lines without

the function output changes

end loop;

storing data.

even when passing the

end if:

same parameters, e..g: when

text file contents change

for i in 0 to 2**NI - 1 loop

readline (IN FILE, BUFF);

read (BUFF, val(i));

end loop;

return val;

end function;

constant LUT val: chunk:= ReadFromFile(file LUT, START POINTER);

begin

```

LUT out <= LUT val (conv integer (LUT in)); The NItoNO LUT behaves like a mux

end structure;