Reconfigurable Computing Research Laboratory

# DIGITAL LOGIC DESIGN VHDL Coding for FPGAs Unit 6

# ✓ FINITE STATE MACHINES (FSMs)

- Moore Machines

- Mealy Machines

- Algorithmic State Machine (ASM) charts

# ✓ FINITE STATE MACHINES (FSMs)

- VHDL Coding: There exist many different

Styles. The style explained here considers two processes: one for the state transitions, and another for the outputs.

- First Step: Have your FSM diagram (ASM preferably) ready. The coding then just simply follows the state diagram.

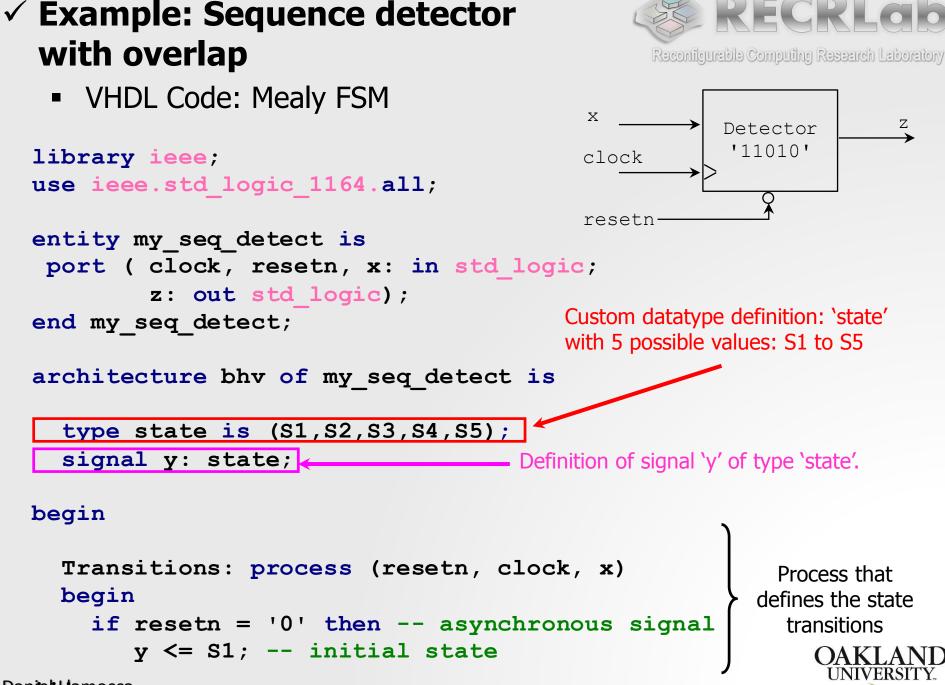

- We need to define a custom user data type (e.g., "state") to represent the states

```

type state is (S1, S2, ... S10) - example with 10 states

signal y: state;

```

We then define a signal of type "state" (e.g. 'y'). In the example, this signal can only take values from S1 to S10.

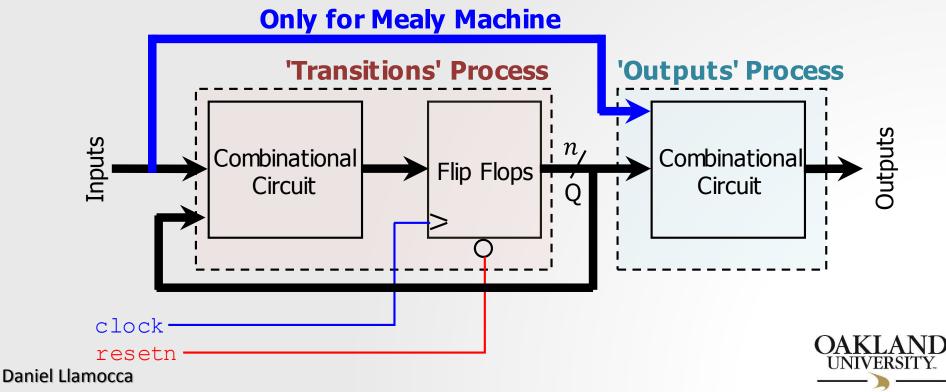

- Two processes must be considered (see figure on next slide)

- ✓ *Transitions*: It is where the state transitions (that occur on the clock edge) are described.

- ✓ Outputs: This is a combinational circuit where outputs are defined based on the current state and input signals. OAKL

## ✓ FINITE STATE MACHINES (FSMs)

### Classification:

**Moore FSM**: Outputs depend only on the current state of the circuit. **Mealy FSM**: Outputs depend on the current state of the circuit as well as the inputs of the circuit.

There should be a '*resetrl*' signal so that the FSM always start from an initial state. The figure depicts a generic state machine with the VHDL processes that describe it.

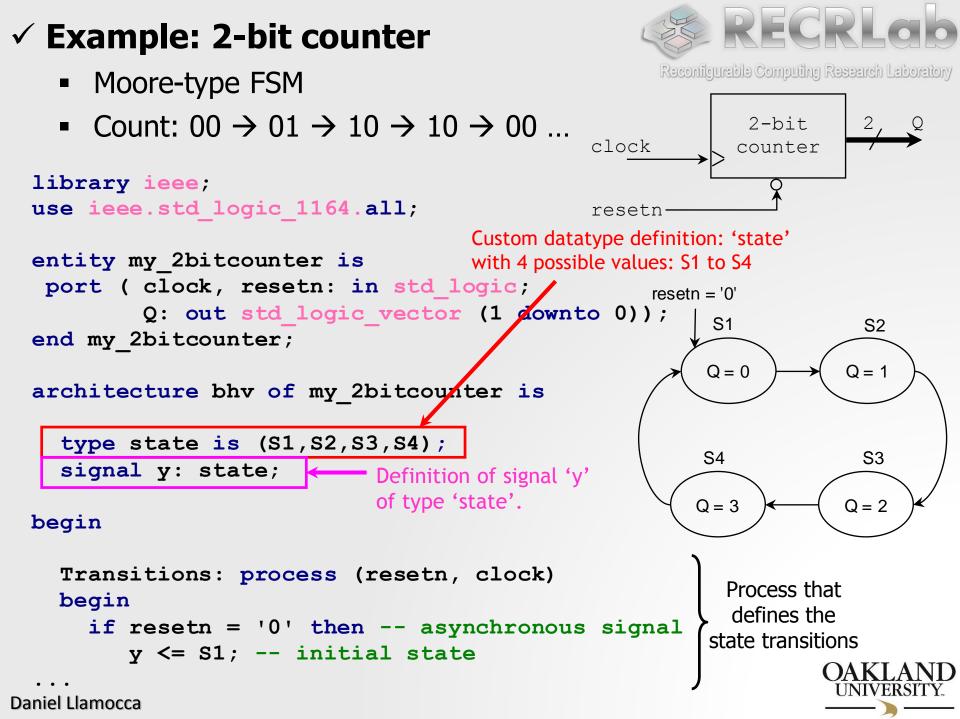

### ✓ Example: 2-bit counter

```

elsif (clock'event and clock='1') then

case y is

when S1 \Rightarrow y \leq S2;

when S2 => y <= S3;

when S3 \Rightarrow y \leq S4;

when S4 \Rightarrow y \leq S1;

end case;

end if;

end process;

Outputs: process (y)

begin

case y is

when S1 => Q <= "00";

when S2 => Q <= "01";

when S3 => Q <= "10";

when S4 \implies Q \iff "11";

end case;

end process;

end bhv;

> my 2bitcounter.zip:

my 2bitcounter.vhd,

tb my 2bitcounter.vhd

Daniel Llamocca

```

Process that defines the state transitions.

Note that the state transitions only occur on the rising clock edge

Note that the outputs only depend on the current state, hence this is a Moore machine

Process that defines the outputs.

Note that the output is not controlled by the clock edge, only by the current state OAKLAN

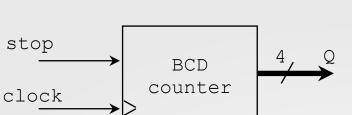

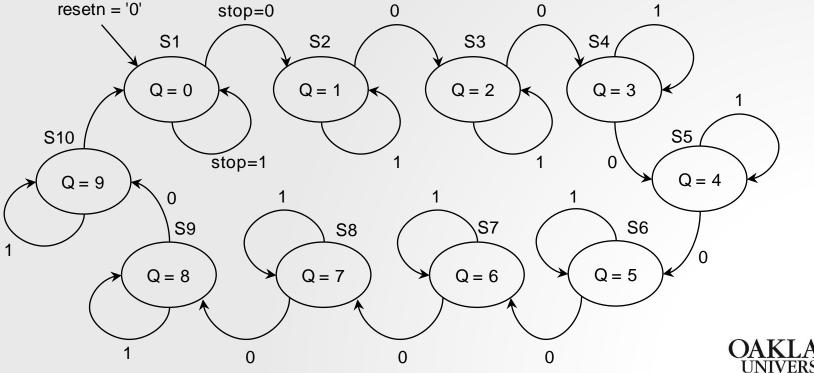

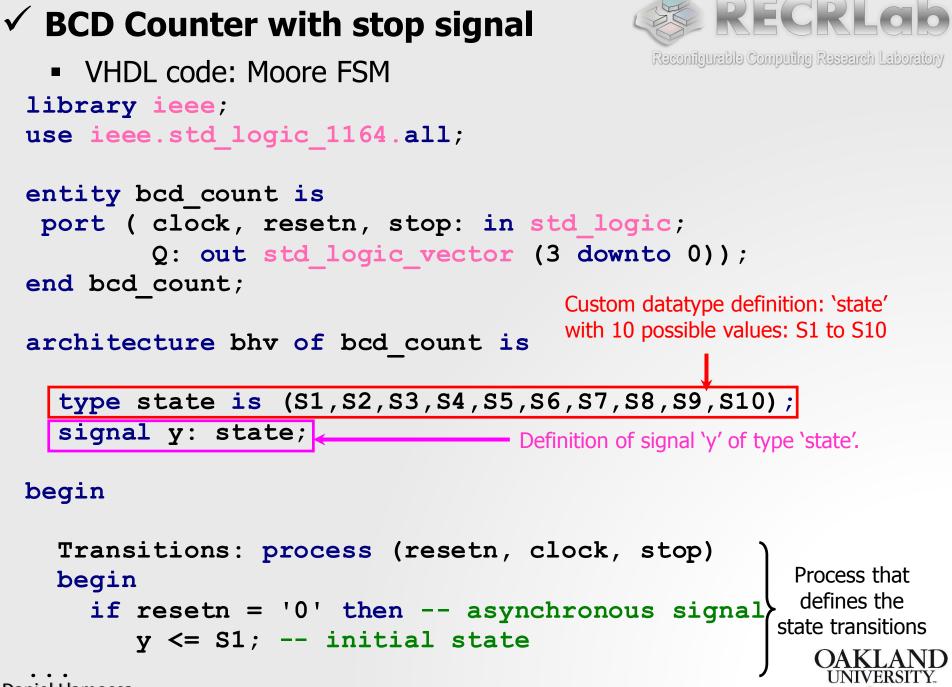

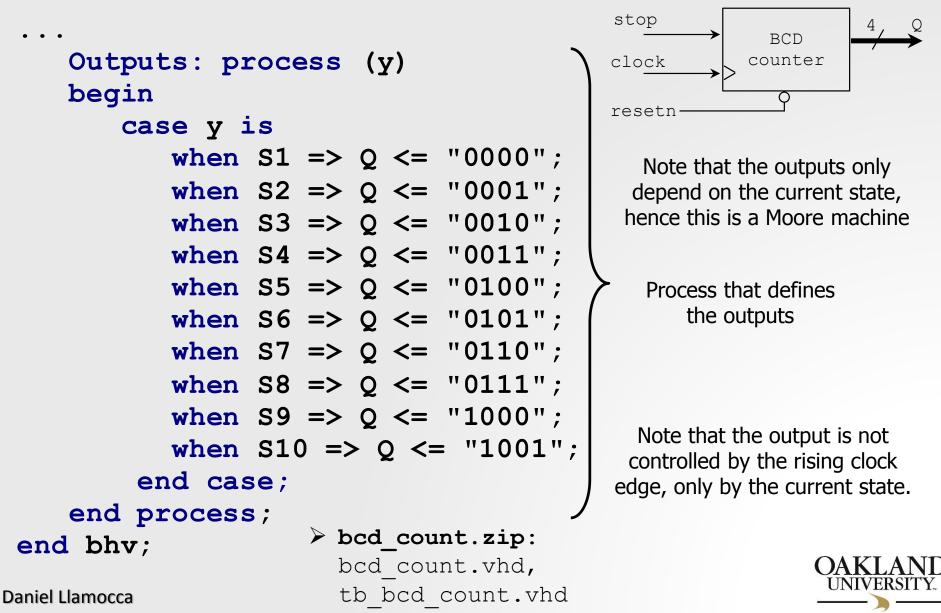

# Example: BCD counter with stop signal

- Moore-type FSM

- If the 'stop' signal is asserted, the count stops. If 'stop' is not asserted, the count continues.

resetn

Reconfigurable Computing Research Laboratory

```

elsif (clock'event and clock='1') then

Reconfigurable Computing Research Laboratory

case y is

when S1 =>

if stop='1' then y<=S1; else y<=S2; end if;

when S2 =>

if stop='1' then y<=S2; else y<=S3; end if;

when S3 =>

if stop='1' then y<=S3; else y<=S4; end if;

when S4 =>

if stop='1' then y<=S4; else y<=S5; end if;

when S5 =>

if stop='1' then y<=S5; else y<=S6; end if;

when S6 =>

if stop='1' then y<=S6; else y<=S7; end if;

when S7 =>

if stop='1' then y<=S7; else y<=S8; end if;

when S8 =>

if stop='1' then y<=S8; else y<=S9; end if;

when S9 =>

if stop='1' then y<=S9; else y<=S10; end if;

when S10 =>

if stop='1' then y<=S10; else y<=S1; end if;</pre>

end case;

end if;

end process;

```

Note that the state transitions depend on the stop signal 'stop'

Process that defines the state transitions

Note that the state transitions only occur on the rising clock edge

• VHDL code:

Reconfigurable Computing Research Laboratory

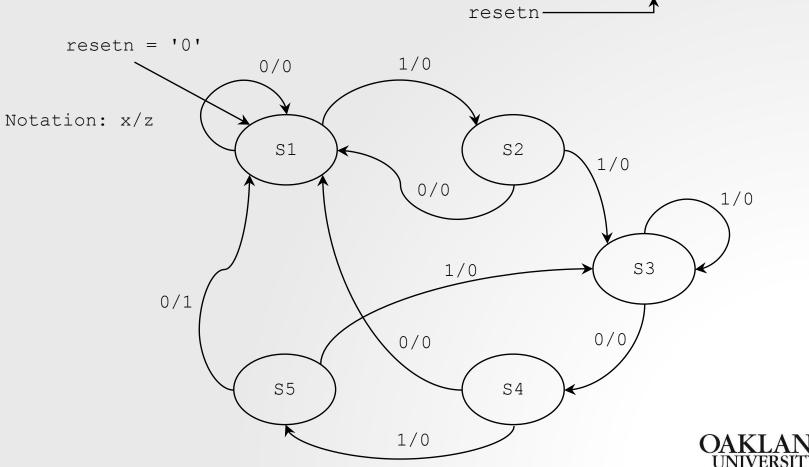

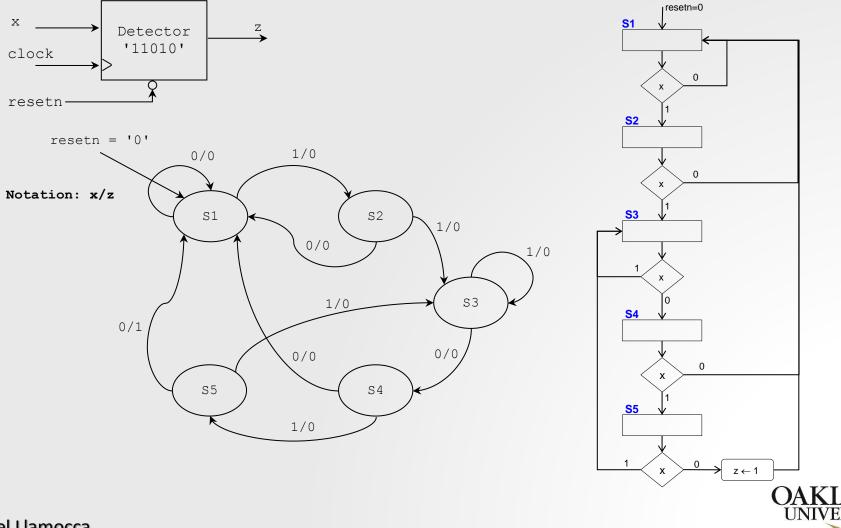

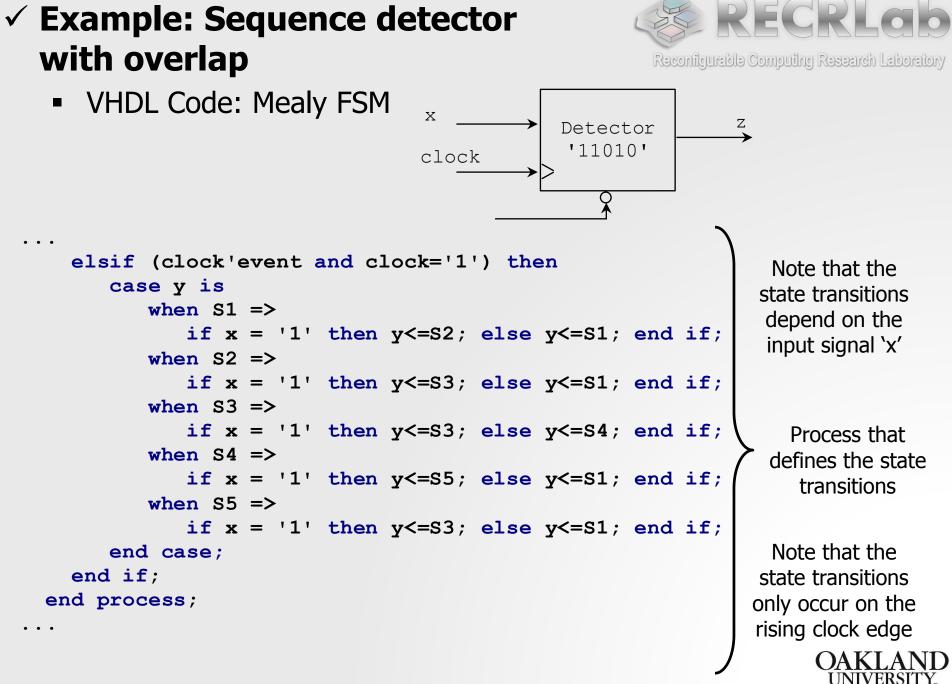

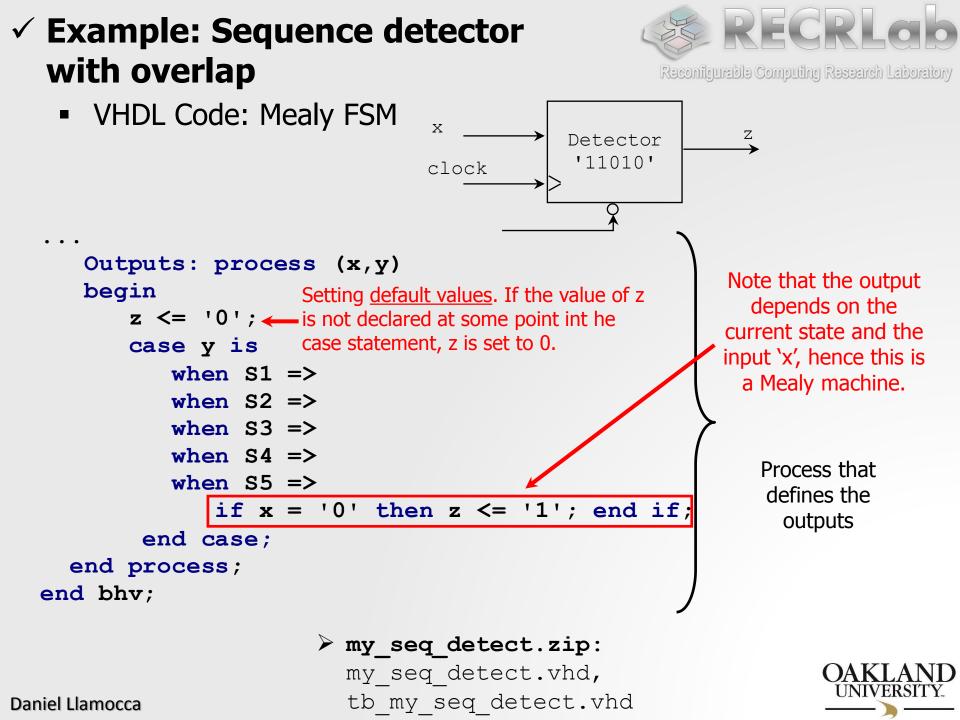

### Example: Sequence detector with overlap

- Mealy-type FSM

- It detects the sequence 11010

- State Diagram: 5 states

Detector

'11010'

Ο

Ζ

Х

clock

### ALGORITHMIC STATE MACHINE (ASMs) charts

- This is an efficient way to represent Finite State Machines.

- We use the 11010 detector as an example here.

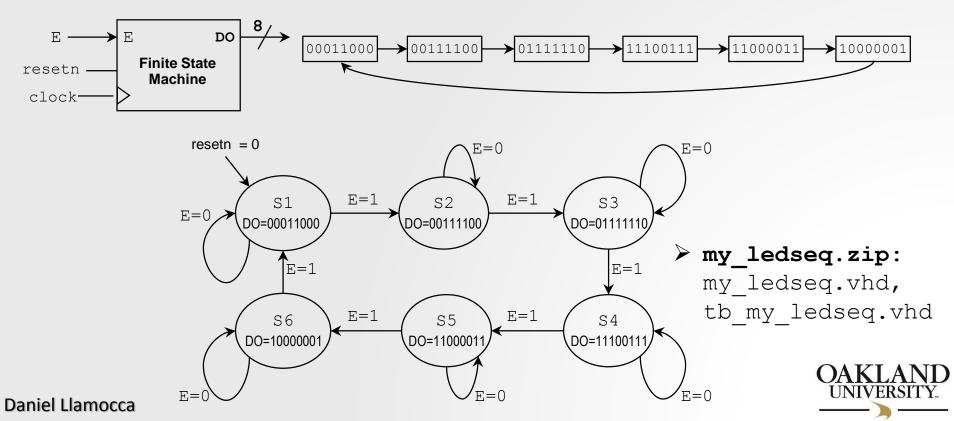

## ✓ Example: LED sequence

Moore-type FSM

- Sequence: 0001100, 00111100, 01111110, 11100111, 11000011, 10000001.

- The FSM includes an enable that allows for state transitions.

- This FSM requires 6 states, i.e. 3 flip flops. The 6-bit output is generated by a combinational circuit (decoder).